# CIRCUIT AND LAYOUT TECHNIQUES FOR SOFT-ERROR-RESILIENT DIGITAL CMOS CIRCUITS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Hsiao-Heng Kelin Lee September 2011

© Copyright by Hsiao-Heng Kelin Lee 2011 All Rights Reserved

| I cert | tify th | at I hav  | re read | this | disserta | tion | and  | that, in  | n my  | opii | nion, | it  |

|--------|---------|-----------|---------|------|----------|------|------|-----------|-------|------|-------|-----|

| is ful | lly ade | quate in  | ı scope | and  | quality  | as a | diss | sertation | n for | the  | degr  | ree |

| of Do  | octor c | of Philos | ophy.   |      |          |      |      |           |       |      |       |     |

(Umran S. Inan) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Ivan R. Linscott)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Christoforos Kozyrakis)

Approved for the University Committee on Graduate Studies

### Abstract

Radiation-induced soft errors are a major concern for modern digital circuits, especially memory elements. Unlike large Random Access Memories (RAM) that can be protected using error-correcting codes and bit interleaving, soft error protection of sequential elements, i.e. latches and flip-flops, is challenging. Traditional techniques for designing soft-error-resilient sequential elements generally address single node errors, or Single Event Upsets (SEU). However, with technology scaling, the charge deposited by a single particle strike can be simultaneously collected and shared by multiple circuit nodes. The likelihood that a soft error caused by multiple circuit node disruptions, or Single Event Multiple Upset (SEMU), happens, increases exponentially as separation between individual transistors decreases. Hence, soft error resilience techniques for sequential elements must focus on Single Event Multiple Upsets (SEMUs).

In this dissertation, we address these concerns by presenting a design framework for soft-error-resilient sequential cell design with an overview of existing circuit and layout techniques for soft error mitigation. In order to address the growing concern over SEMUs, we introduce a new soft error resilience layout design principle called LEAP, or Layout Design through Error-Aware Transistor Positioning, which targets SEMUs by using circuit interactions and transistor placement to improve the soft error performance of a circuit without significant area cost. As an example of circuit and layout co-design for soft error resilience, we discuss our application of LEAP on the SEU-immune Dual Interlocked Storage Cell (DICE) by implementing a new sequential element layout called LEAP-DICE. LEAP-DICE retains the original DICE circuit topology, but employs a layout design efficient at using transistor interactions

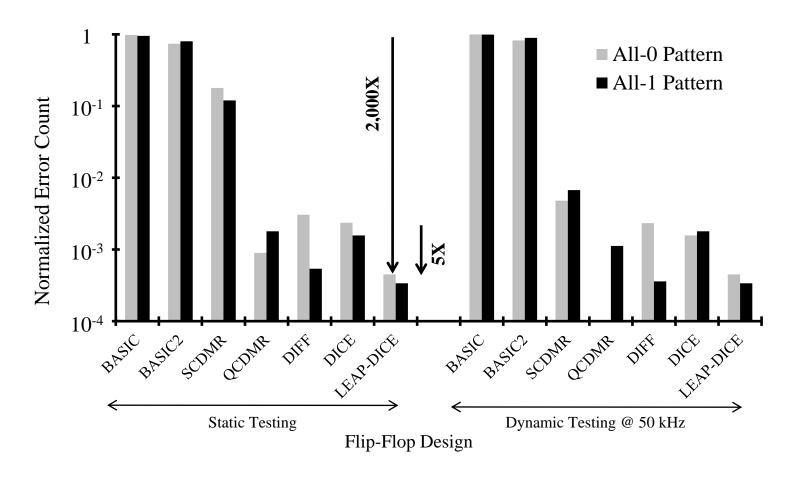

to reduce SEMUs. After comparing the soft error performance of SEU-immune flip-flops with the LEAP-DICE flip-flop with a test chip in 180nm CMOS under 200–MeV proton radiation, we conclude that

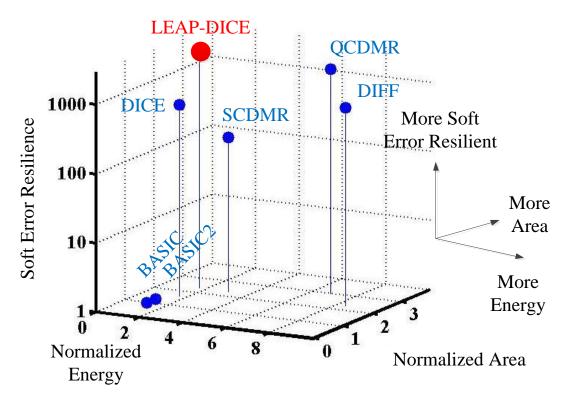

- Our LEAP-DICE flip-flop achieved the best soft error performance among all SEU-immune flip-flop designs we investigated. LEAP-DICE encounters on average 2,000X fewer errors compared to the reference D flip-flop.

- Our LEAP-DICE flip-flop encounters 5X fewer errors compared to the DICE flip-flop, while both designs share identical circuit topology and transistor sizing. LEAP-DICE imposes negligible power and delay costs and 40% area cost compared to the DICE design.

- In the evaluation of our design framework, we also discovered new soft error effects related to operating conditions such as voltage scaling, clock frequency setting and radiation dose.

## Acknowledgement

Throughout my graduate studies at Stanford, I have had the privilege of working with exceptional people, teachers and students alike. Although I am closing this chapter of my life and moving forward, I will always cherish the good times we had together.

First, I would like to first thank my advisors, Prof. Umran Inan and Dr. Ivan Linscott, for offering me the unique opportunity of working on an independent research project, for giving me the freedom to explore various research ideas, for providing the support to continue my studies, and for always believing in me. I have not been the easiest student to mentor, but you have always been patient with me.  $Tesekk\ddot{u}r$  ederim.

I would also like to thank Prof. Christos Kozyrakis for chairing my oral defense committee and serving as the third reader for this dissertation.

I am heavily indebted to Prof. Subhasish Mitra, who acted as a mentor and supporter for my work in soft errors, and who introduced me to the art of writing papers. Prof. Mitra was instrumental in helping me complete this work. Without Prof. Mitra, I would still be languishing in the abyss of graduate school (figuratively and literally speaking, given that I worked in the basement of the electrical engineering building for many unspeakable years).

I would like to thank the various people who have given me technical guidance and support in the field of soft errors, notably Dr. Klas Lilja and Mounaim Bounasser of Robust Chip, and Norbert Seifert and Min Zhang of Intel. This work was heavily sponsored by Robust Chip and inspired by Dr. Lilja's vision of using layout as a design dimension for soft-error-resilient circuit design.

I cannot forget the essential support of the administrative staff: Shaolan Min,

Helen Niu, and Uma Mulukutla, who always made sure that students have sufficient funding support, and enough to get by from day to day.

For two years, I had the chance to take part on the WIPER project, where I worked with Dr. Jack Doolittle, Robert Bumala and Clem Tillier from Lockheed Martin, and Dr. Dave Lauben from Stanford. Their collaboration was instrumental in contributing to my understanding of how to design satellite instrument.

I also would thank Dr. Bennett Wilburn and Prof. Mark Horowitz for the opportunity to be part of the Light Field Camera project during my first two years at Stanford. This experience gave me a peek at doing top notch independent research at Stanford.

I am blessed to have a chance to work with exceptional peers at Stanford, namely Dr. Charles Wang and Dr. Benjamin Mossawir, former students of the Stanford VLF Group, who supported me at critical times in test chip tapeout, and offered helpful suggestions for radiation hardening ideas and radiation testing setup. I would also like to thank Prasanthi Relangi, Rakesh Gnana David Jeyasingh and Jumie Yuventi for helping me on my radiation experiments at New Mexico and Indiana. I would also thank other members of the VLF Group: Jeff Chang (whose board testing support was critical), Carsten Barth (whose late night company I enjoyed), former occupants of my Packard 037 basement office (including Dr. Robert Moore, Dr. Joe Payne, Dr. Ryan Said and Dr. Ben Cotts), and other fellow current and former members of the Stanford VLF Group and Stanford Robust Systems Group.

Finally, I would like to thank my family, my father Eric, my mother Grace, and my brother Ben. No words can express the love and gratitude I feel for my family. At times I have almost given up, and without their support, I would not have had the courage and determination to find myself again.

HSIAO-HENG "KELIN" LEE

Stanford, California August 26, 2011 This work was sponsored by the following contracts and agencies:

- NASA New Technology Initiatives Program, Grant No. NAG5-10822.

- The Aerospace Corporation Subcontract No. 46000001624-9.

- Air Force Research Laboratory, Contract No. AFRL FA8718-05-C0027.

- Defense Threat Reduction Agency/Robust Chip Inc., Contract No. HDTRA1-09-P0011.

- National Science Foundation.

This research was also made possible with generous fabrication support from National Semiconductor Corporation, as well as radiation testing support from Los Alamos National Laboratory and Indiana University Cyclotron Facility.

## Contents

| $\mathbf{A}$ | bstra | act                                       | iv |

|--------------|-------|-------------------------------------------|----|

| $\mathbf{A}$ | ckno  | wledgement                                | vi |

| 1            | Intr  | roduction                                 | 1  |

|              | 1.1   | A Brief Overview of Soft Errors           | 2  |

|              | 1.2   | Purpose                                   | 3  |

|              | 1.3   | Contributions                             | 4  |

|              | 1.4   | Organization                              | 4  |

| 2            | Rac   | liation Effects in Electronics            | 6  |

|              | 2.1   | Single-Event Effects                      | 6  |

|              |       | 2.1.1 Soft Errors                         | 8  |

|              |       | 2.1.2 Hard Errors                         | 8  |

|              | 2.2   | Sources of Radiation                      | 9  |

|              |       | 2.2.1 Near-Earth Radiation Environment    | 9  |

|              |       | 2.2.2 Terrestrial Radiation Environment   | 10 |

|              | 2.3   | Total Dose Effects                        | 15 |

|              | 2.4   | Conclusion                                | 15 |

| 3            | Circ  | cuit Soft Error Resilience Techniques     | 17 |

|              | 3.1   | Soft Error Generation                     | 18 |

|              | 3.2   | RC-Based Soft Error Resilience Techniques | 21 |

|              | 3.3   | Triple Modular Redundancy                 | 25 |

|   | 3.4 | Dual I                        | Modular Redundancy                                           | 27  |  |  |  |  |

|---|-----|-------------------------------|--------------------------------------------------------------|-----|--|--|--|--|

|   |     | 3.4.1                         | C-Element Based Soft-Error-Resilient Latches                 | 27  |  |  |  |  |

|   |     | 3.4.2                         | Dual Interlocked Storage Cell (DICE)                         | 33  |  |  |  |  |

|   |     | 3.4.3                         | Differential Cascode Voltage Switch Logic (DCVSL)            | 34  |  |  |  |  |

|   | 3.5 | SEMU                          | Vulnerability in SEU-Immune Techniques                       | 35  |  |  |  |  |

|   | 3.6 | Concl                         | usion                                                        | 38  |  |  |  |  |

| 4 | Lay | out So                        | oft Error Resilience Techniques                              | 39  |  |  |  |  |

|   | 4.1 | Charg                         | e Collection in CMOS Circuits                                | 40  |  |  |  |  |

|   | 4.2 | Tradit                        | tional Layout Techniques for Charge Collection Mitigation    | 44  |  |  |  |  |

|   |     | 4.2.1                         | Guard Rings, Guard Contacts and Guard Drains                 | 45  |  |  |  |  |

|   |     | 4.2.2                         | Node Separation                                              | 50  |  |  |  |  |

|   | 4.3 | Layou                         | t Design through Error-Aware Transistor Positioning (LEAP) . | 52  |  |  |  |  |

|   | 4.4 | LEAP                          | P-DICE: A Case Study                                         | 59  |  |  |  |  |

|   | 4.5 | Conclu                        | usion                                                        | 69  |  |  |  |  |

| 5 | Tes | t Chip                        | Implementation                                               | 71  |  |  |  |  |

|   | 5.1 | Proces                        | ss Selection                                                 | 72  |  |  |  |  |

|   | 5.2 | General Test Chip Description |                                                              |     |  |  |  |  |

|   | 5.3 | Test C                        | Chip Implementation Details                                  | 76  |  |  |  |  |

|   |     | 5.3.1                         | Standard Cell Layout Style                                   | 77  |  |  |  |  |

|   |     | 5.3.2                         | Standard Cell Library                                        | 84  |  |  |  |  |

|   |     | 5.3.3                         | I/O Cells                                                    | 85  |  |  |  |  |

|   |     | 5.3.4                         | Flip-Flop Designs under Test                                 | 89  |  |  |  |  |

|   |     | 5.3.5                         | Clock Generation and Distribution                            | 104 |  |  |  |  |

|   | 5.4 | Conclu                        | usion                                                        | 105 |  |  |  |  |

| 6 | Exp | erime                         | ntal Setup and Results                                       | 106 |  |  |  |  |

|   | 6.1 | Radia                         | tion Experimental Setup                                      | 107 |  |  |  |  |

|   | 6.2 | Radia                         | tion Experimental Results                                    | 113 |  |  |  |  |

|   |     | 6.2.1                         | Neutron Testing                                              | 113 |  |  |  |  |

|   |     | 622                           | Proton Tosting                                               | 116 |  |  |  |  |

|                           | 6.3 Conclusion      | 122 |

|---------------------------|---------------------|-----|

| 7                         | Conclusion          | 124 |

|                           | 7.1 Future Research | 125 |

| $\mathbf{B}_{\mathbf{i}}$ | ibliography         | 127 |

## List of Tables

| 3.1 | Overview of circuit-level techniques for soft error resilience                                                                    | 23       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----------|

|     | Conditions to produce single-event transients in CMOS circuits Two-node SEMU combinations and possible protective node selection. |          |

|     | Normalized performance comparison for various flip-flop designs Test chip I/O voltage settings                                    | 74<br>88 |

## List of Figures

| 2.1  | Charge generation and collection                                        | 7  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Parasitic PNPN structure leading to single event latchup                | 10 |

| 2.3  | Theoretical sea-level cosmic rays                                       | 12 |

| 3.1  | Pulse models for single event transients                                | 20 |

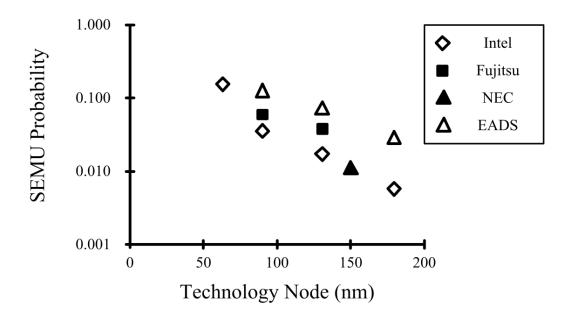

| 3.2  | Comparison of published SEMU probabilities                              | 20 |

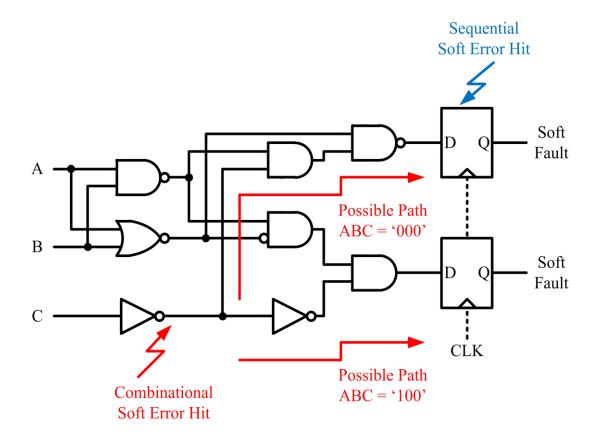

| 3.3  | Combinational and sequential soft errors                                | 21 |

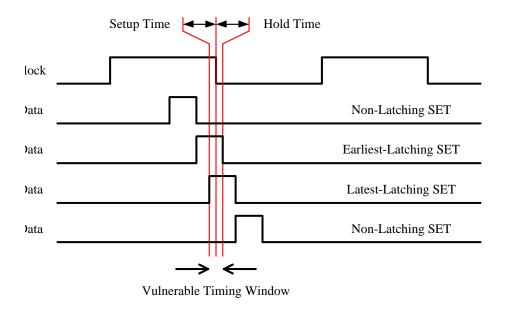

| 3.4  | Vulnerable timing window for combinational SETs                         | 22 |

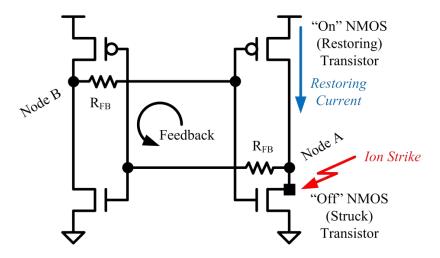

| 3.5  | SEU response model in an SRAM cell                                      | 24 |

| 3.6  | RC-hardened SRAM cells                                                  | 25 |

| 3.7  | Triple modular redundancy latches                                       | 26 |

| 3.8  | The C-Element                                                           | 28 |

| 3.9  | SET filtering of a latch input using C-Element                          | 29 |

| 3.10 | Single C-Element Dual Modular Redundancy (SCDMR) flip-flop              | 30 |

| 3.11 | Built-In Soft Error Resilience (BISER) flip-flop                        | 31 |

| 3.12 | Delay filtering in the feedforward path of soft-error-resilient latches | 32 |

| 3.13 | Single Event Resistant Topology (SERT) latch                            | 34 |

| 3.14 | Dual Interlocked Storage Cell (DICE)                                    | 35 |

| 3.15 | Differential Cascode Voltage Switch Logic (DCVSL)                       | 36 |

| 3.16 | SEMU in the Dual Interlocked Storage Cell (DICE)                        | 37 |

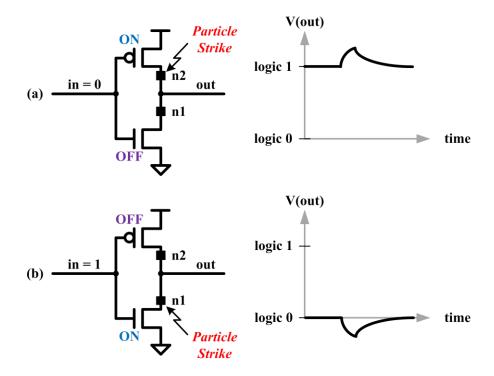

| 4.1  | Particle strike on the drain contact node of an "OFF" transistor in an  |    |

|      | inverter                                                                | 41 |

| 4.2  | Particle strike on the drain contact node of an "ON" transistor in an |    |

|------|-----------------------------------------------------------------------|----|

|      | inverter                                                              | 42 |

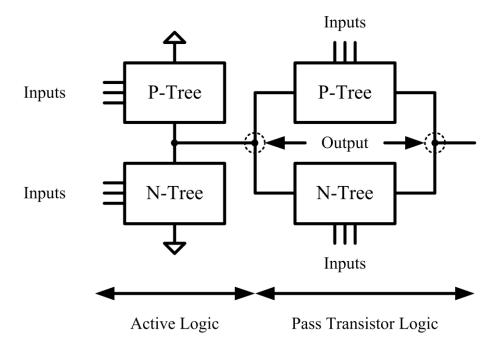

| 4.3  | Static CMOS logic design                                              | 43 |

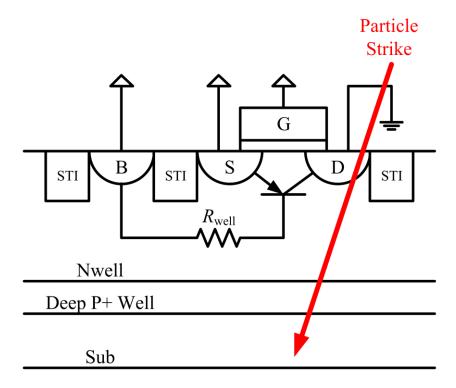

| 4.4  | Bipolar parasitic conduction in an "OFF" PMOS transistor activated    |    |

|      | by a radiation strike                                                 | 46 |

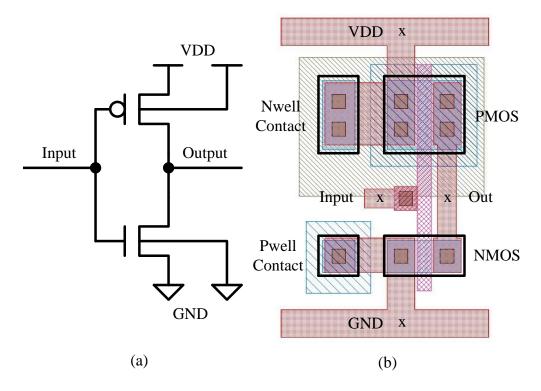

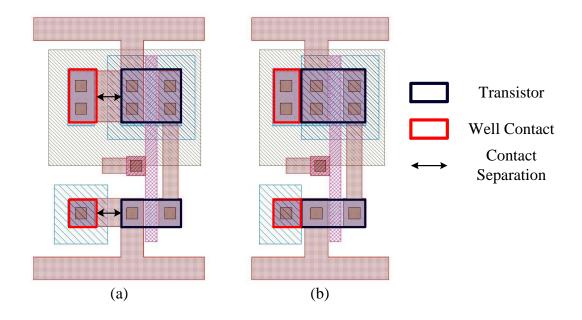

| 4.5  | Well contacts in CMOS cell layout                                     | 47 |

| 4.6  | Well contact styles in CMOS inverter cell layout                      | 48 |

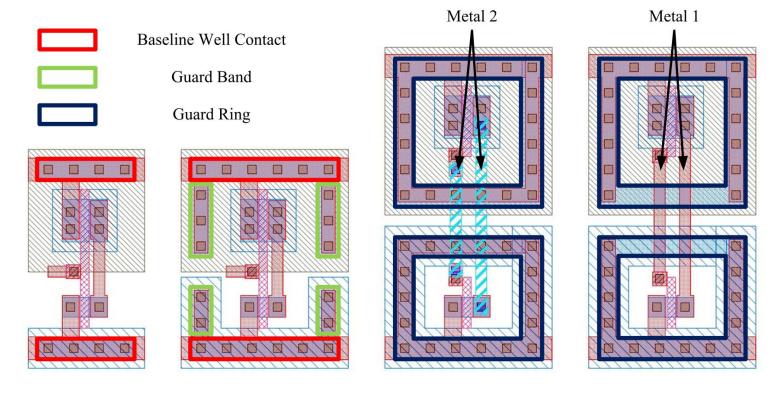

| 4.7  | Guard bands and guard rings in CMOS inverter cell layout              | 49 |

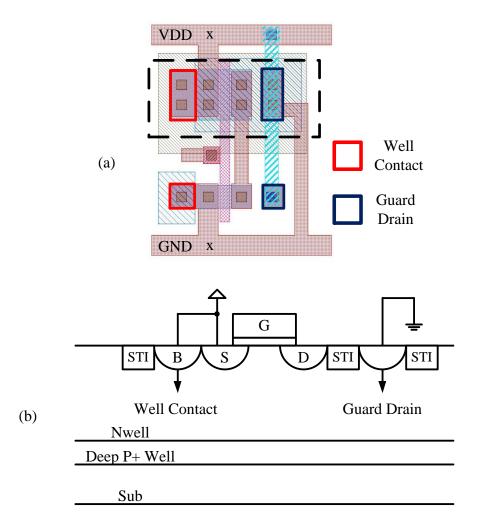

| 4.8  | Guard drains in CMOS layout                                           | 50 |

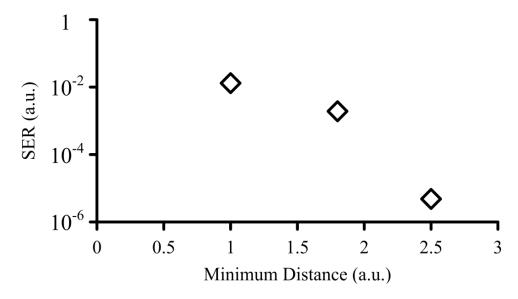

| 4.9  | Soft error rate dependence on node separation                         | 51 |

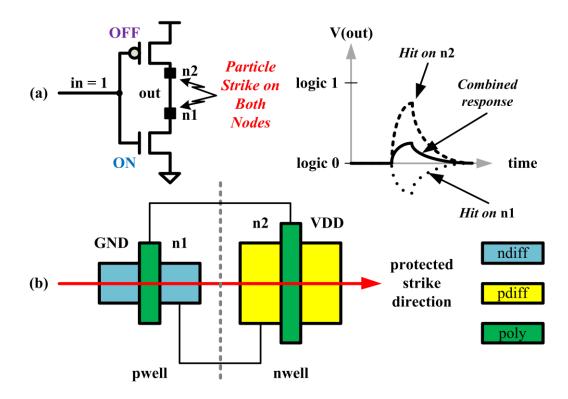

| 4.10 | LEAP principle for an inverter through transistor alignment           | 53 |

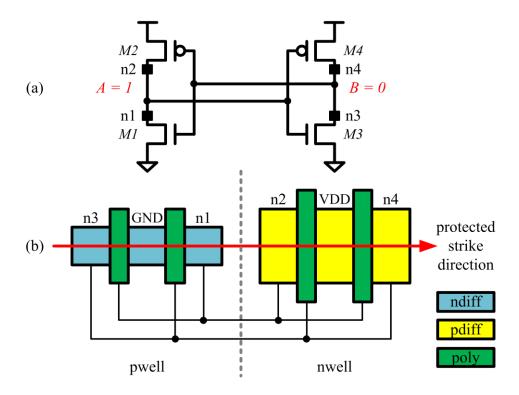

| 4.11 | LEAP principle for a cross-coupled inverter pair                      | 55 |

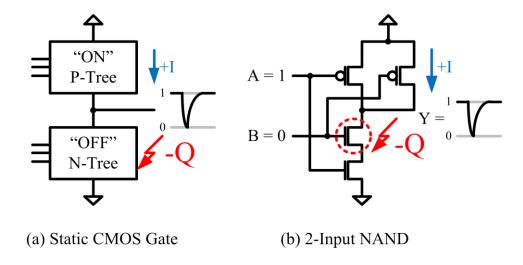

| 4.12 | Radiation-induced charge collection on the "OFF" transistor tree of a |    |

|      | static CMOS gate.                                                     | 56 |

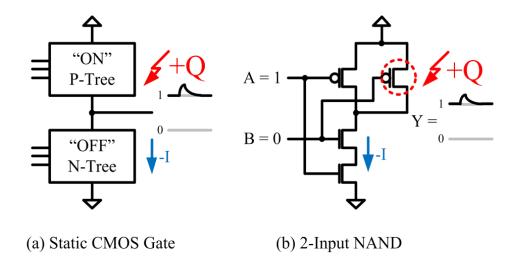

| 4.13 | Radiation-induced charge collection on the "ON" transistor tree of a  |    |

|      | static CMOS gate.                                                     | 57 |

| 4.14 | Single-event transient suppression in a CMOS gate using the LEAP      |    |

|      | principle                                                             | 58 |

| 4.15 | Single-event charge collection in the Dual Interlocked Storage Cell   |    |

|      | (DICE)                                                                | 60 |

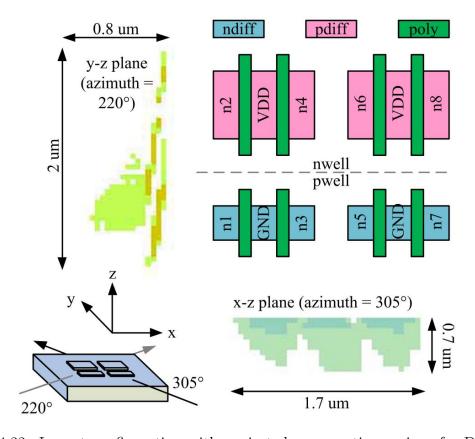

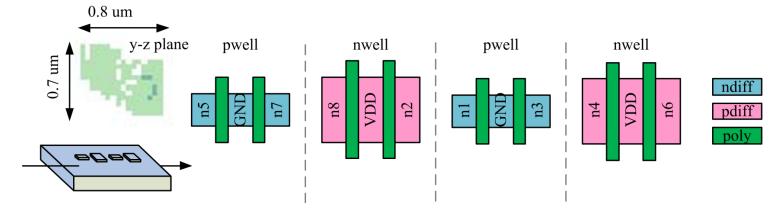

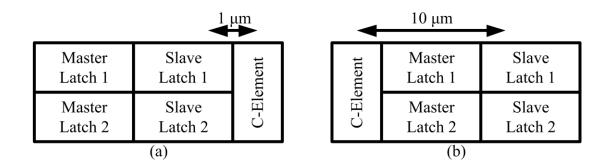

| 4.16 | Two DICE layout configurations                                        | 62 |

| 4.17 | LEAP-DICE layout with the SEMU example highlighted                    | 62 |

| 4.18 | Alternate DICE layout                                                 | 63 |

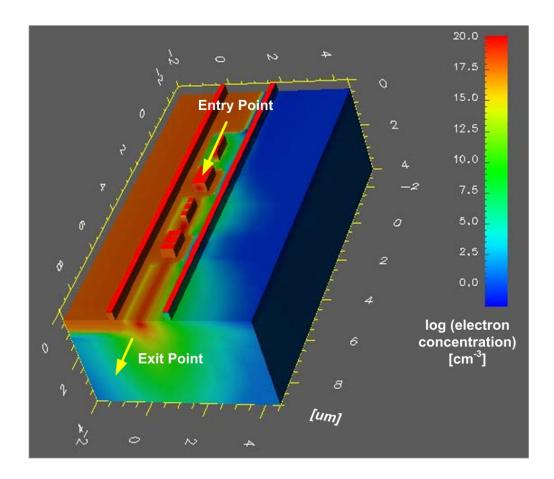

| 4.19 | Simulation "snapshot" for the LEAP-DICE latch structure               | 64 |

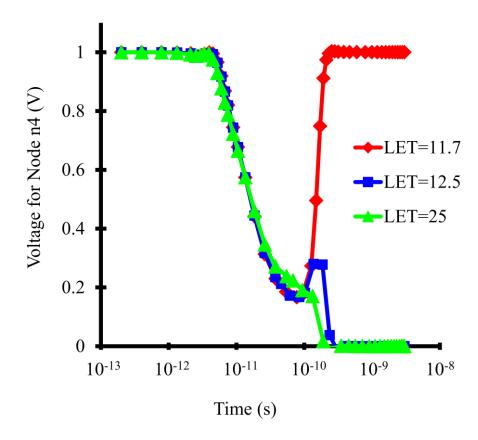

| 4.20 | Simulated DICE output voltage with different LET levels               | 65 |

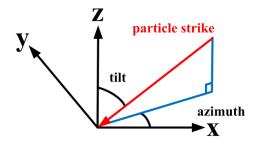

| 4.21 | Coordinate system for particle strike directions                      | 66 |

| 4.22 | Layout configuration with projected cross-section regions for DICE    | 66 |

| 4.23 | Layout configuration with projected cross-section regions for LEAP-   |    |

|      | DICE                                                                  | 67 |

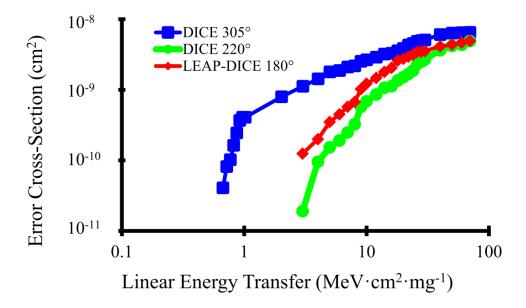

| 4.24 | Error cross-section comparison of DICE and LEAP-DICE as a function    |    |

|      | of LET.                                                               | 68 |

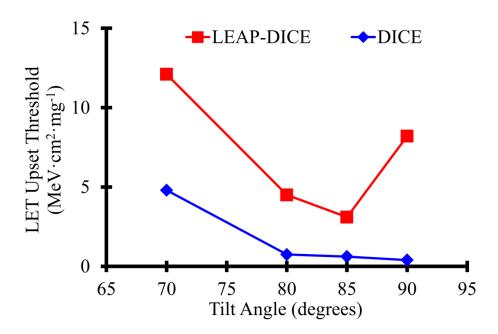

| 4.25 | LET upset threshold as a function of tilt angle                       | 69  |

|------|-----------------------------------------------------------------------|-----|

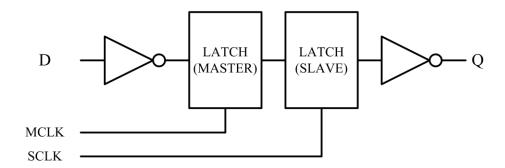

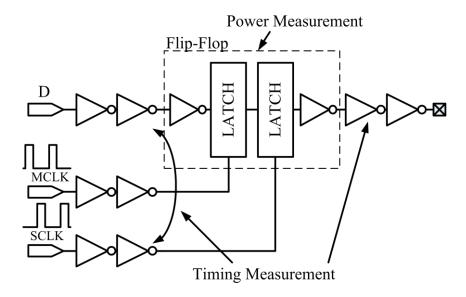

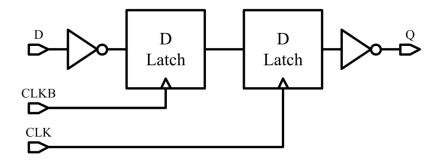

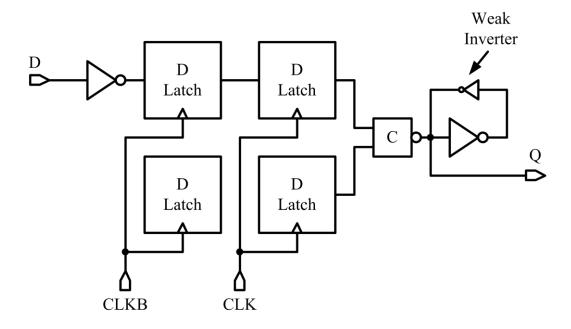

| 5.1  | Master-slave flip-flop configuration                                  | 73  |

| 5.2  | Simulation test bench for post-layout timing and power measurements.  | 75  |

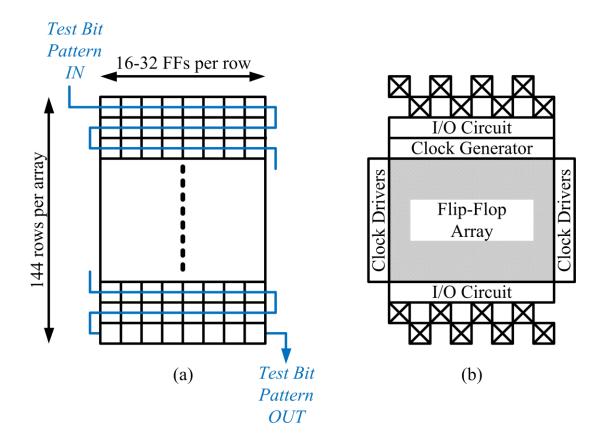

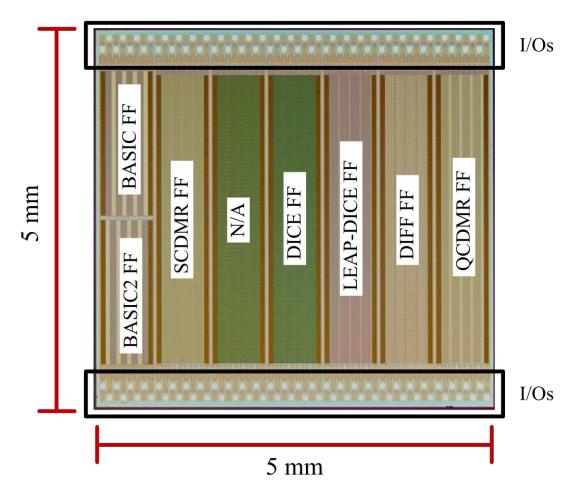

| 5.3  | Test chip organization                                                | 76  |

| 5.4  | Die photograph of the 180nm bulk test chip                            | 77  |

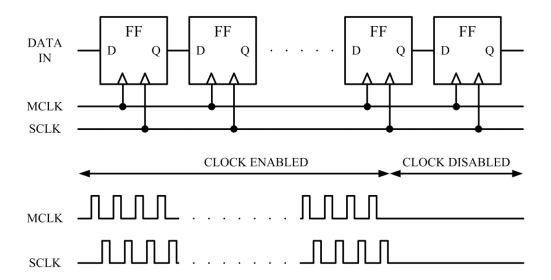

| 5.5  | Test chip clocking scheme                                             | 78  |

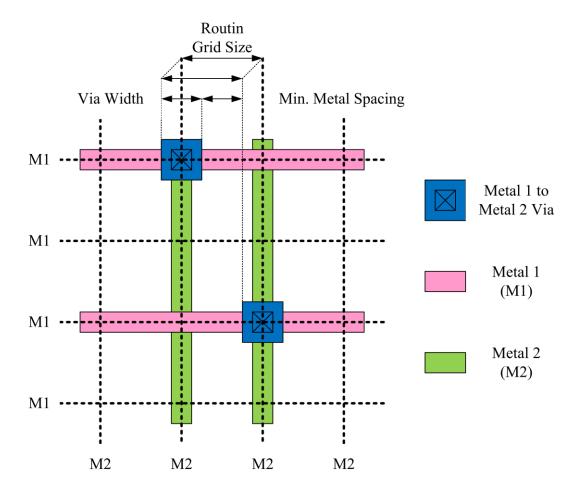

| 5.6  | Routing grid example                                                  | 80  |

| 5.7  | Standard cell inverter layout example                                 | 81  |

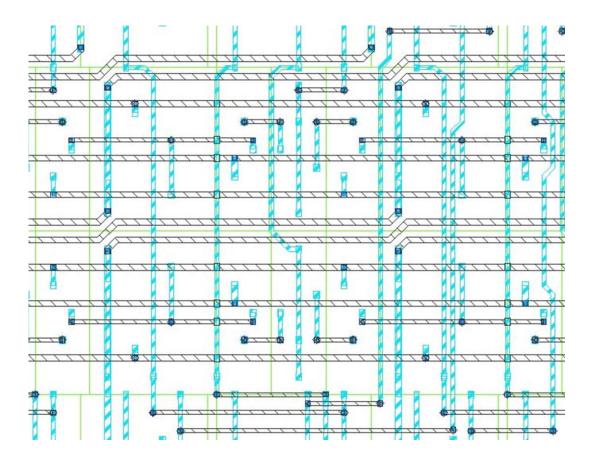

| 5.8  | Complex routing example                                               | 82  |

| 5.9  | Total dose current leakage effect on standard two-edged vs. enclosed- |     |

|      | geometry transistors                                                  | 83  |

| 5.10 | Enclosed-geometry transistor layout                                   | 84  |

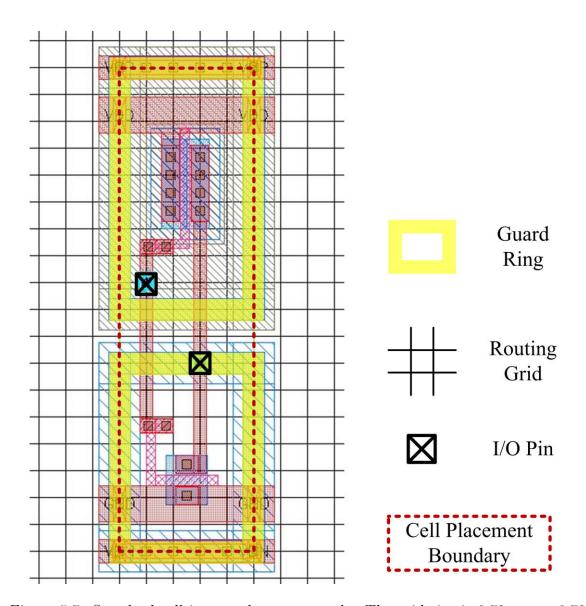

| 5.11 | I/O cell structure                                                    | 86  |

| 5.12 | ESD protection circuit                                                | 87  |

| 5.13 | Level-down shifter                                                    | 89  |

| 5.14 | Two-stage level-up shifter                                            | 90  |

| 5.15 | Staggered-pitch pad placement                                         | 91  |

| 5.16 | Circuit symbols                                                       | 92  |

| 5.17 | Standard "BASIC" D flip-flop                                          | 93  |

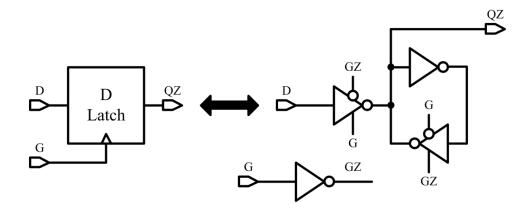

| 5.18 | Standard D latch                                                      | 93  |

| 5.19 | SCDMR flip-flop                                                       | 94  |

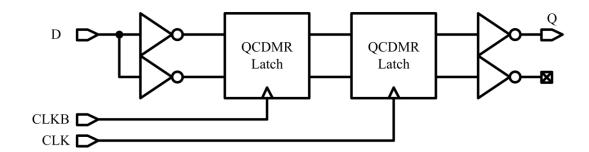

| 5.20 | QCDMR flip-flop                                                       | 95  |

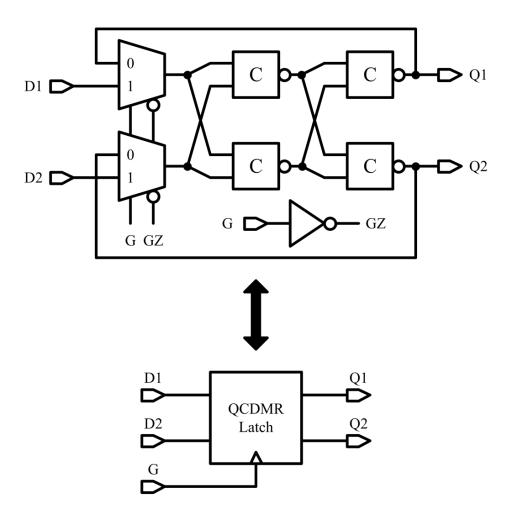

| 5.21 | QCDMR latch                                                           | 96  |

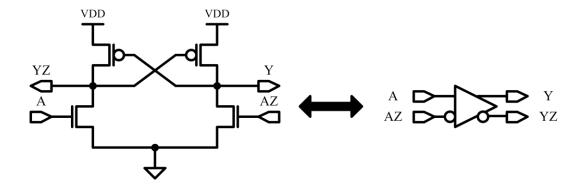

| 5.22 | DCVSL inverter                                                        | 97  |

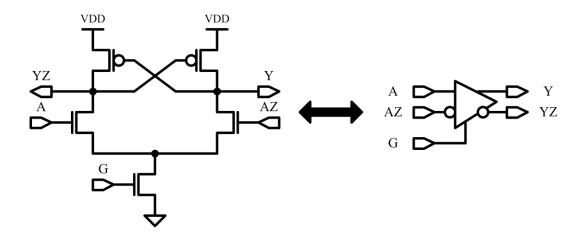

| 5.23 | Clocked DCVSL inverter                                                | 97  |

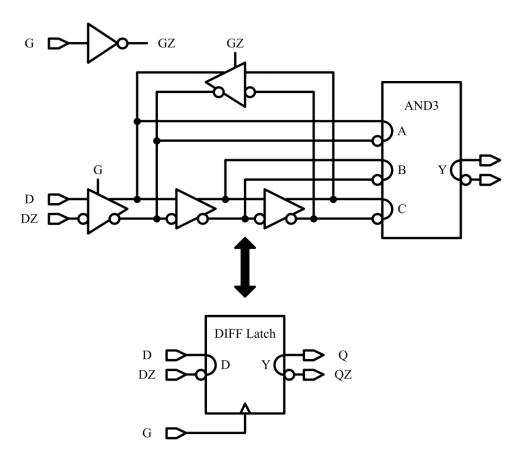

| 5.24 | DCVSL latch                                                           | 98  |

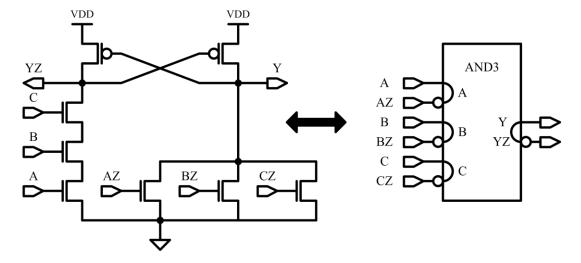

| 5.25 | Three-input DCVSL AND gate                                            | 99  |

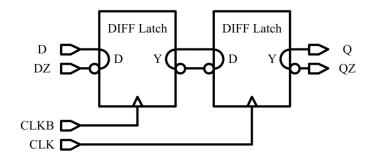

| 5.26 | DCVSL "DIFF" flip-flop                                                | 99  |

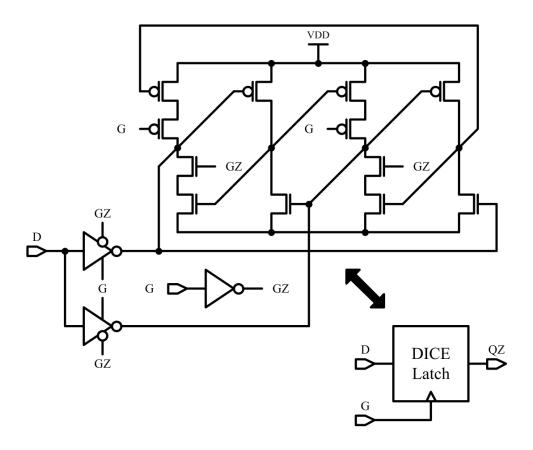

| 5.27 | Clocked "DICE" latch                                                  | 100 |

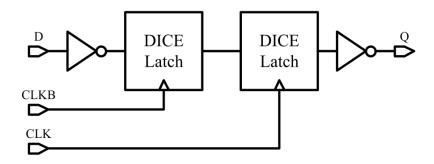

| 5.28 | "DICE" D flip-flop                                                    | 100 |

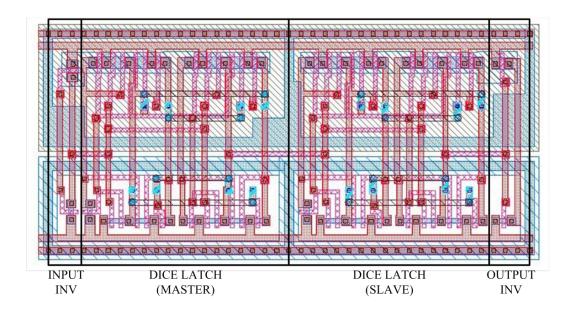

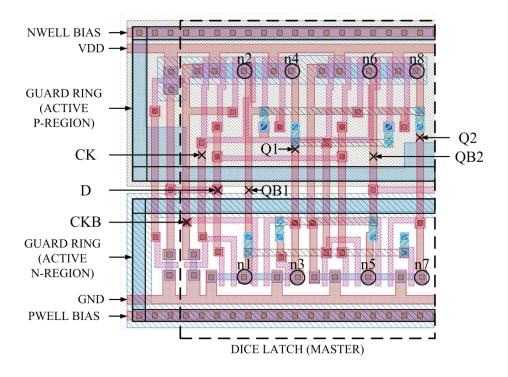

| 5.29 | "DICE" D flip-flop layout                                                 | 101 |

|------|---------------------------------------------------------------------------|-----|

| 5.30 | Close-up of the clocked "DICE" latch layout                               | 101 |

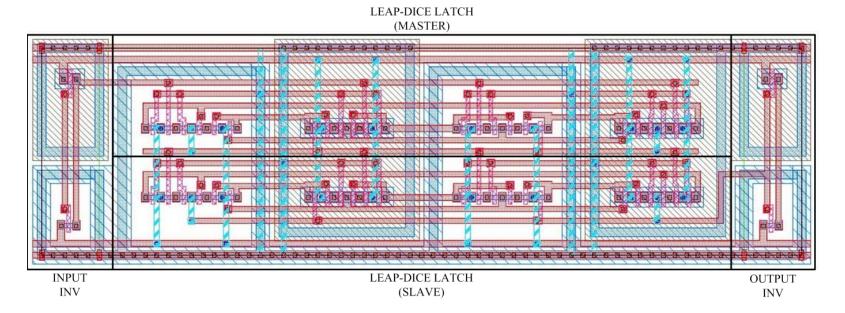

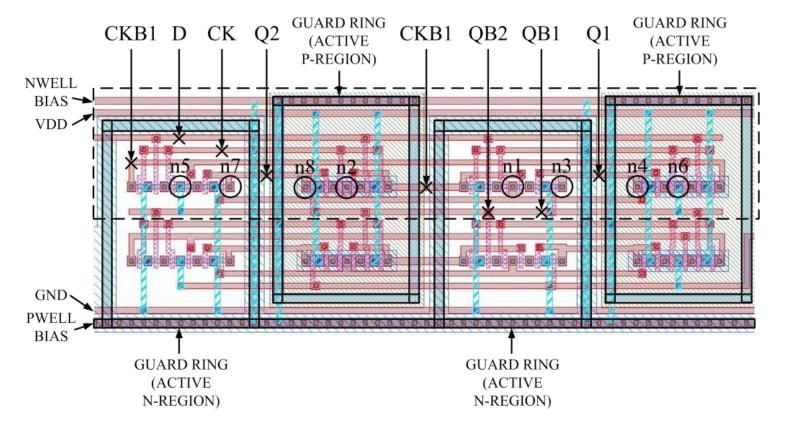

| 5.31 | "LEAP-DICE" flip-flop layout                                              | 102 |

| 5.32 | Close-up of the clocked "LEAP-DICE" latch layout                          | 103 |

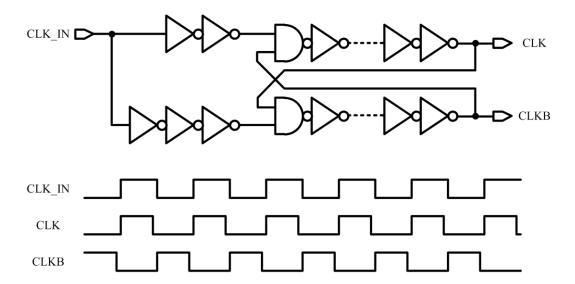

| 5.33 | Non-overlapping clock generation                                          | 104 |

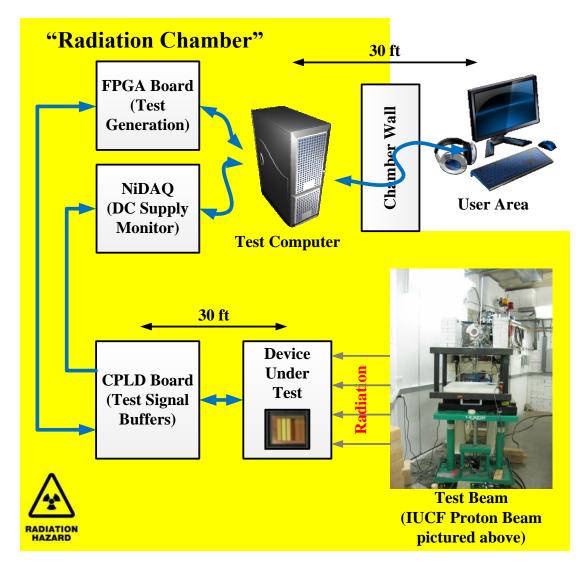

| 6.1  | Test environment for integrated circuits radiation testing                | 109 |

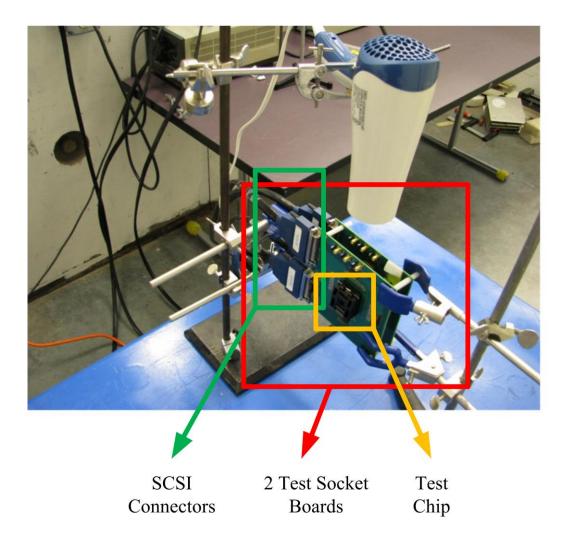

| 6.2  | Test chip socket board                                                    | 110 |

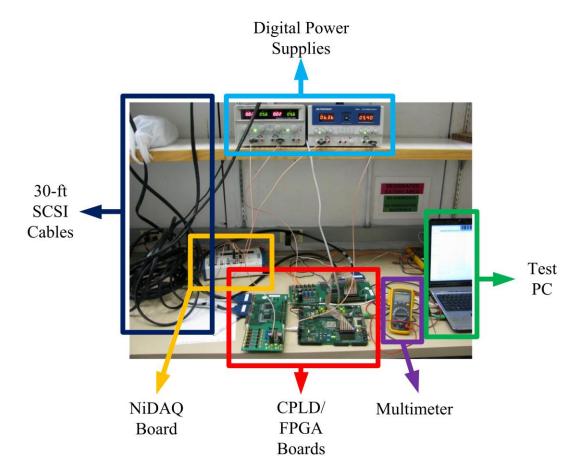

| 6.3  | Test bench setup located away from the radiation beam                     | 111 |

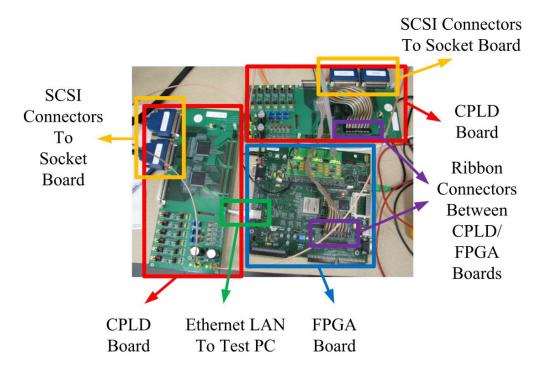

| 6.4  | Close-up of FPGA and CPLD boards                                          | 112 |

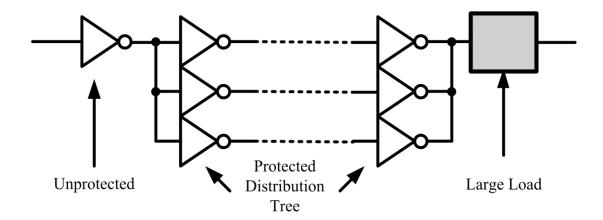

| 6.5  | Neutron beam profile at Los Alamos National Laboratory                    | 114 |

| 6.6  | Clock tree protection against soft errors                                 | 116 |

| 6.7  | Measured soft error performance of flip-flops at 1V                       | 118 |

| 6.8  | SCDMR layout placement                                                    | 119 |

| 6.9  | SCDMR frequency dependence                                                | 120 |

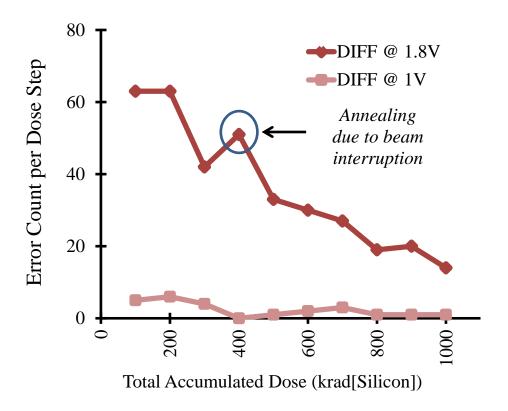

| 6.10 | Soft error reduction in the DIFF design with increasing radiation dose.   | 122 |

| 6.11 | Design framework of soft-error resilient flip-flops in the "energy — area |     |

|      | — soft-error-resilience" space                                            | 123 |

## Chapter 1

## Introduction

The year was 2000. Mysterious computer server crashes started to plague internet and telecommunications companies across the United States. The server crashes happened on high-end servers made by Sun Microsystems, and the server disruptions were serious enough that they received substantial media coverage [Lyons, 2000]. The root cause: Soft Errors.

What are soft errors? In electronics, a soft error occurs when a signal or datum suddenly becomes corrupted due to charge deposition produced by an energetic particle strike. The data corruption is not a persistent phenomenon, and the system can normally function if it is allowed to reset itself or recover from a previous state. Therefore, a soft error happens infrequently and is difficult to reproduce. In the case of Sun Microsystems, infrequent data corruption by cosmic rays (i.e. atmospheric neutrons and protons) in the unprotected cache memory of the affected servers was identified as the root cause for the mysterious server crashes. And Sun was not the only semiconductor company affected by soft errors. A series of soft error warnings was also issued by Cisco for its networking switches, and now Cisco has dedicated customer support related to soft errors in their products [Cisco Systems Inc., 2005].

#### 1.1 A Brief Overview of Soft Errors

Soft errors in electronics have been directly observed starting from the 70s. It was first theorized by Wallmark and Marcus [1961] that silicon device dimensions would be eventually limited to 10  $\mu$ m by cosmic rays. Then reports of cosmic-ray-induced upsets came in space electronics in 1975 by  $Binder\ et\ al.$  [1975]. Soon, cosmic-neutron-induced upsets at the ground level were recorded in the Cray-1 computer at Los Alamos National Laboratory in 1976 [Normand et al., 2010], followed by accounts of alpha-particle-related upsets in dynamic random memories (DRAM) three years later [May and Woods, 1979]. Dodd and Massengill [2003] gave a detailed history of soft errors in electronics. Benedetto [1998] also described the challenge of electronics facing soft errors in space applications.

In recent years, as transistor dimensions have scaled down to deep submicron levels, transistors become more and more sensitive to charge collection due to particle strikes. While major progress in the development of soft error resilience techniques allowed the soft error rate in silicon memory and sequential cells to fall [Borucki et al., 2008], technology scaling also means that more transistors than ever are packed within the same unit area, and the soft error improvement per memory cell has not been keeping pace with the exponential growth of transistor density. As a result, overall soft error rate per chip has rapidly increased, and is now a major reliability concern for microprocessors [Karnik and Hazucha, 2004; Baumann, 2005; Meaney et al., 2005; Mitra et al., 2005; Seifert, 2007; Sanda et al., 2008; Gill et al., 2009; Dixit and Heald, 2009; Dixit and Wood, 2011].

The first soft error hardening efforts were developed in the 1980s, and focused on hardening large random access memory (RAM) arrays to prevent or correct soft errors in stored memory cells, either through static random access memory (SRAM) cell hardening [e.g., Andrews et al., 1982; Weaver et al., 1987] or error correction codes [e.g., Hsiao, 1970; Chen and Hsiao, 1984]. May et al. [1984] discovered that propagation of glitches in combinational logic produced by particle strikes can also lead to soft errors. However, the contribution of soft errors in combinational logic was not substantial enough at the time, and most efforts were concentrated on the design

of robust sequential elements. The development of soft-error-resilient SRAM cells [e.g., Diehl et al., 1982; Weaver et al., 1987] later leads to soft-error-resilient latch designs such as the Rockett Cell [Rockett, 1988], the Whitaker Cell [Whitaker et al., 1991] and the Dual Interlocked Storage Cell (DICE) [Calin et al., 1996]. Redundancy techniques such as Triple Modular Redundancy and Double Modular Redundancy soon followed [Mavis and Eaton, 2002; Mitra et al., 2005; Shuler et al., 2005].

#### 1.2 Purpose

The design techniques for designing soft-error-resilient sequential elements, described in the previous subsection, generally address single errors caused by Single-Event Upsets (SEUs), where charge collection in one circuit node due to a particle strike can flip the value of the memory bit stored. However, with technology scaling, the charge deposited by a particle strike can be simultaneously collected and shared by multiple circuit nodes in the same well [Olson et al., 2005; Seifert, 2007; Amusan et al., 2008. In addition to charge sharing, the particle strike direction also determines how much charge is deposited, as well as charge distribution among multiple nodes [Amusan et al., 2006; Baze et al., 2008]. When the incoming particle is a proton or neutron, interactions between the incident particle and the silicon nucleus can produce secondary particles generating multiple ionization tracks [Koga, 1996]. A Single-Event Multiple Upset (SEMU) happens when one energetic particle generates charge collection in multiple circuit nodes resulting in a soft error [Dodd and Massengill, 2003. As device dimensions shrink, the probability of SEMUs increases exponentially, and previous techniques focusing on single node upsets are not as effective against SEMUs. Hence soft error resilience techniques for sequential elements must focus on SEMUs. Since SEMUs have a geometric dependence on circuit layout, the main focus of this work is to bring in integrated circuit layout, specifically the placement of individual transistors, as a new design dimension to mitigate SEMUs in addition to existing circuit and layout techniques for soft error resilience.

#### 1.3 Contributions

The primary contribution of this dissertation is as follows:

• We demonstrated the first silicon implementation of the LEAP layout principle for soft error resilience in digital circuits with the new LEAP-DICE flip-flop. LEAP, or *Layout Design through Error-Aware Transistor Positioning*, is a layout design principle that relies on transistor placement and transistor interactions within the circuit to reduce the overall single event circuit response. LEAP-DICE has the best soft error performance among existing circuit techniques with moderate area and power cost, and achieves 2,000X soft error resilience compared to the standard D flip-flop.

The development of the LEAP-DICE flip-flop also leads to other contributions:

- We developed a framework for soft-error-resilient sequential cell design, by quantifying the performance trade-offs of circuit and layout resilience techniques in the soft-error-resilience power delay area design space. We experimentally demonstrate the success of this framework with a comprehensive evaluation in silicon of representative circuit and layout techniques using an 180nm CMOS test chip. In this framework, we also introduced a simple yet easy-to-use metric called *Soft Error Resilience*, to evaluate the robustness of different circuit designs operating under the same conditions.

- We also discovered new soft error effects related to circuit operating conditions such as supply voltage, total radiation dose and clock frequency. From these observations, we concluded that design for soft error resilience must target circuit operating conditions over the lifetime of the application.

#### 1.4 Organization

This chapter provided a brief history of the discovery of soft errors in electronics as a primer for research in soft errors. It then described the earlier development

of soft error resilience techniques. With growing concern over SEMUs as a result of technology scaling, we decided to address this problem by developing a new soft-error-resilient cell called LEAP-DICE using a combination of circuit and layout techniques. The new sequential cell design and the preparation of an effective design framework to evaluate this cell, form the basic of this work.

To familiarize the reader with radiation effects in electronics, we describe various sources of radiation as well as their short-term and long-term effects on electronics in Chapter 2. Chapter 3 provides an overview on existing circuit-level soft-error-resilience techniques. After briefly discussing existing layout techniques, Chapter 4 introduces the new LEAP layout design principle for soft error resilience, then implements the new LEAP-DICE design created from the application of this layout principle on the SEU-immune DICE circuit topology. The resulting sequential cell design is both SEU-immune and SEMU-resilient.

In order to evaluate the soft error performance of the new LEAP-DICE flip-flop, we created a test chip containing the new design, plus a baseline design and additional SEU-immune flip-flop designs inspired from existing circuit techniques to form a basis for comparison. Chapter 5 discusses the design and implementation of the 180nm CMOS test chip. Our experimental procedures and results obtained from accelerated radiation testing at Los Alamos National Laboratory and Indiana University Cyclotron Facility are reported in Chapter 6. Finally, Chapter 7 completes this dissertation by reviewing the major contributions of this work and offers new insights into possible future research in soft errors. A bibliography of all references is included at the end to facilitate the reading of this work.

## Chapter 2

## Radiation Effects in Electronics

As transistors become smaller and smaller with technology scaling, they become more sensitive to temporary disruptions caused by energetic particle strikes from the surrounding environment. These disruptions, called Single-Event Effects, are of great concern for the reliable operation of deep submicron electronic circuits. Single-event effects can cause soft errors, where loss or corruption of data occurs but the circuit can operate correctly if allowed to reset, and hard errors, where the circuit can become permanently damaged. This chapter starts with a discussion on how single-event effects can disturb circuit operation, then continues with various radiation sources capable of producing energetic particles causing soft errors along with different types of radiation particles of concern. Although long-term exposure effects, called Total-Dose Effects, are not of concern in terrestrial environment, they can impact electronics under accelerated radiation testing (used to estimate the soft error performance within a short period of time), and are briefly discussed in this chapter, followed by conclusions.

#### 2.1 Single-Event Effects

When an energetic particle from the environment hits silicon, it can generate charge through *direct ionization* or *indirect ionization*. Direct ionization happens when the particle bounces off outer electrons of silicon atoms in its traveling path, generating

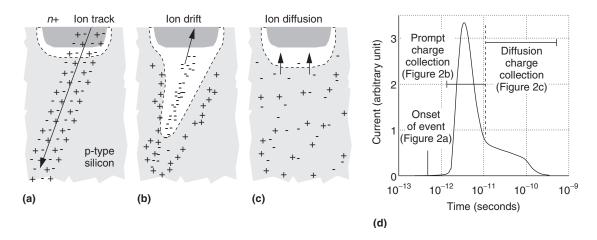

Figure 2.1: Charge generation and collection from *Baumann* [2005, Figure 2].

electron-hole pairs in its wake. Indirect ionization happens when a small-size particle interacts with the silicon nucleus to produce various by-products such as heavy ions or charged particles, which can in turn produce charge through direct ionization.

During direct ionization, the energetic particle can create disturbance in the form of Linear Energy Transfer (LET), or kinetic energy loss per unit length. LET is often expressed in units of energy per distance such as MeV/cm, or MeV·cm<sup>2</sup>/mg when normalized by the density of the material [JEDEC Standard, 1996]. In silicon, every 3.6eV of energy lost produces one electron-hole pair, and charge collection of 1 to 100s of fC often occurs within a few microns of a reverse-bias silicon junction.

As an energetic ion strikes in the vicinity of a reverse-biased silicon junction, electron-hole pairs form around the particle track, where most of the charge generation is concentrated in a cylindrical form. Right after the onset of the event, charge collection rapidly occurs near the depletion region of the silicon junction by drift action within a nanosecond, followed by slower charge collection from diffusion. The overall result is a current pulse shown in Figure 2.1. If the particle strikes in a silicon region where no electric field is present, the electrons and holes generated will not move by drift or diffusion, and will recombine in place, resulting in no charge collection. Baumann [2005] offers a detailed explanation of the charge collection process.

Energetic particle strikes can cause both soft errors (temporary disruption of data)

or hard errors (permanent hardware failure). The following subsections discuss their causes and behaviors.

#### 2.1.1 Soft Errors

In the event that a particle strike results in charge collection in a circuit node in a digital circuit, the circuit node voltage can momentarily change. If the magnitude of this voltage is large enough, a Single-Event Transient (SET, also called a glitch) can happen. The equivalent amount of charge required to be collected is called Critical Charge, often labeled as  $Q_{\text{crit}}$  [Dodd and Sexton, 1995]. If the SET is allowed to propagate and persist in a digital circuit, it can create a Soft Error, an erroneous change (or upset) in the state of the circuit. On one hand, a Single-Event Upset (SEU) is a soft error with only one transistor diffusion node affected by charge collection. On the other hand, a Single-Event Multiple Upset (SEMU) occurs when a particle strike affects multiple transistor diffusion nodes and causes a soft error. The Soft Error Rate (SER), is the rate at which a device or system encounters or is expected to encounter soft errors. It can be expressed as either the number of Failtures-In-Time (FIT), or as Mean Time Between Failures (MTBF). FIT is characterized in units of number of errors per billion hours (1 FIT = 1 error per  $10^9$  hours). MTBF is measured in terms of number of hours between individual failures (1 MTBF = 114,077 FIT). Please note that a "failure" is not equivalent to a "soft error", since a soft error may not result in the overall system failure, and multiple soft errors may be required to induce a system failure.

#### 2.1.2 Hard Errors

In addition to creating soft errors, single particle strikes can sometimes have long lasting and potentially damaging effects. If the particle energy is sufficiently large, it can create a *Single-Event Gate Rupture* (SEGR), where the electric field across the transistor gate oxide becomes large enough to exceed the critical breakdown field allowed. The result of the oxide breakdown is a permanent short circuit through the oxide. Interestingly enough, the device scaling of transistor oxide thickness actually

increases the electric field tolerance for oxide breakdown [Sexton et al., 1997; Massen-gill et al., 2001]. SEGR is not a concern for modern CMOS processes at the ground level.

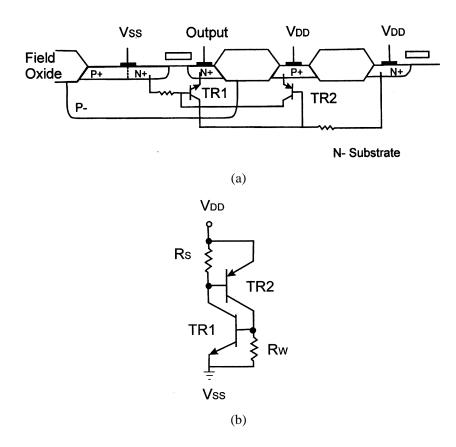

Single-Event Latchup (or SEL) is another potential catastrophic failure mechanism caused by energetic particles [Leavy and Poll, 1969]. When a particle strikes in the vicinity of two neighboring PMOS and NMOS transistors, it can activate the parasitic PNPN structure formed by the NMOS-PMOS pair (see Figure 2.2). The activated parasitic PNPN structure provides a short impedance path between the power and ground of the circuit and creates a short circuit current run-off, potentially destroying transistors in the vicinity. Once latchup occurs, the only way to remove this condition is through power cycling (i.e. turning off the power supply then turning it back on). Latchup can be prevented by properly insulating each individual transistor at the process level, or by following proper integrated circuit layout rules by placing supply contacts or guard rings (acting as low-resistance paths to supplies) near transistors (see Section 4.2.1). Some silicon processes containing good isolation such as Siliconon-Insulator (SOI) are thus inherently resistant to latchup. [Sexton, 2003] provides a detailed review of the various destructive single-event effects found in semiconductor devices. Please note that hard errors are not the focus of this work. This work primarily deals with soft errors in the terrestrial environment.

#### 2.2 Sources of Radiation

Soft errors are caused by particles from radiation sources in the environment. The following subsections detail different sources of radiation causing soft errors in electronics.

#### 2.2.1 Near-Earth Radiation Environment

The Near-Earth environment is home to a host of energetic charged particles around Earth held in place by the Earth's magnetic field. Most of these particles originate from either the solar wind or cosmic rays. Particles trapped in this region are mostly

Figure 2.2: Parasitic PNPN structure leading to single event latchup from *Sexton* [2003]. (a) Cross-section of a bulk CMOS technology on n-substrate material. (b) Equivalent circuit.

electrons and protons as well as heavy ions [Walt, 1994; Hareyama et al., 2007]. In this study, we do not consider electronics operating in space.

#### 2.2.2 Terrestrial Radiation Environment

Radiation affecting electronics in the terrestrial environment mainly comes from three sources: alpha particles, high-energy cosmic rays and low-energy cosmic rays [Baumann, 2005]. To evaluate the soft error resilience of a system, it is possible to perform an accelerated testing using a concentrated radiation source to mimic the actual radiation dose received during its lifetime of operation. The accelerated radiation testing

can predict actual field soft error performance lasting several years in a short amount of time (typically minutes to hours) in laboratory setting. However, devices under irradiation can become damaged by the high intensity of the radiation source, and the soft error rate measured from this process can deviate from the actual field behavior.

The following subsections describe various forms of radiation sources in the terrestrial environment, along with the availability of accelerated testing for these radiation sources.

#### Alpha Particles

Alpha particles, as a major source of soft errors in electronics, were first observed in the 1970s in DRAM memories [May and Woods, 1979]. An alpha particle consists of a nucleus formed by two neutrons and two protons, and is emitted by the nuclear decay of unstable radioactive isotopes such as Uranium-238 ( $^{238}$ U) or Thorium-232 ( $^{232}$ Th) in packaging, and Lead-210 ( $^{210}$ Pb) in solder. Alpha particles are mostly produced at energy levels of less than 10 MeV [Baumann, 2005], and can create charge through direct or indirect ionization. Since an alpha particle is positively charged, it creates an ionizing path when it travels through silicon until it loses all its energy (being "stopped"). In silicon, the traveling range of a 10-MeV alpha particle is less than 100  $\mu$ m. Therefore, only alpha particles produced close to the silicon die (i.e. from packaging) can cause soft errors. Alpha particles used to be of great concern, but can be mitigated by making sure packaging material is not contaminated with radioactive isotopes.

To perform accelerated alpha-particle testing on integrated circuits, one can simply place a thin radioactive foil such as Californium-252 ( $^{252}$ Cf) directly over the silicon die [Koga, 1996].

#### Neutrons

Atmospheric neutrons are also a major source of soft errors in electronics. When cosmic rays reach the Earth's atmosphere, they produce a chain of nuclear interactions with the atmosphere, producing muons, protons, neutrons and pions reaching sea level

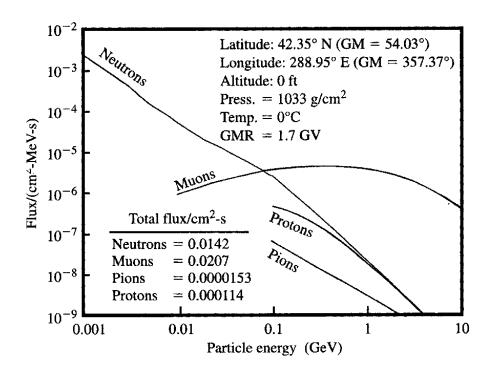

Figure 2.3: Theoretical sea-level cosmic rays from Ziegler [1998].

[Ziegler and Lanford, 1980]. Figure 2.3 shows the distribution of cosmic ray particles at ground level. Among the cosmic ray particles found, neutrons are the main source of soft errors, as electronic chips cannot be well shielded from the cosmic neutron flux using conventional means (metal shielding, better shielding materials etc.): one foot of concrete can barely reduce the neutron flux by a factor of 1.4 [Dirk et al., 2003]. The neutron flux depends on the altitude: going from sea level to 10,000 feet, the neutron flux increases by about 10X.

Since neutrons have no charge themselves, they can only generate charge through indirect ionization by interacting with silicon nuclei or nuclei of other elements (dopants or metal) present in the chip [Baumann, 2005]. When a neutron collides with the nucleus of an atom, it can break the nucleus into multiple fragments (inelastic collision) or displace it (elastic collision). The fragments or recoil products can become a lighter ion with additional smaller particles (neutrons, protons or alpha particles), and they will move through silicon by bouncing off outer electrons of neighboring atoms in their ionization path before being completely stopped in silicon.

Low-energy neutrons, or thermal neutrons, tend to be absorbed through inelastic collision. Most importantly, very low energy neutrons ( $\ll 1$  MeV) can interact with the Boron implant found in semiconductor doping. Boron naturally occurs with two isotopes: Boron-11 ( $^{11}$ B, 80.1% abundance) and Boron-10 ( $^{10}$ B, 19.9% abundance). The  $^{10}$ B isotope is unstable in the presence of neutrons, and has a reaction cross-section three to seven orders of magnitude higher than other isotopes found in semiconductor materials. When a  $^{10}$ B nucleus absorbs a thermal neutron, it breaks apart into an excited Lithium-7 ( $^{7}$ Li) recoil nucleus and an alpha particle capable of inducing soft errors. The  $^{10}$ B isotope can be found as p-type silicon doping implant and as implant in the BPSG dielectric layer, but its occurrence is three orders of magnitude more likely in BPSG than in silicon implant doping. For conventional processes containing BPSG, BPSG is the main source of soft errors due to boron reactions. It is possible reduce SER due to  $^{10}$ B activation by eliminating the BPSG layer in the silicon processes, or by enriching BPSG with  $^{11}$ B isotope [Baumann and Hossein, 1995].

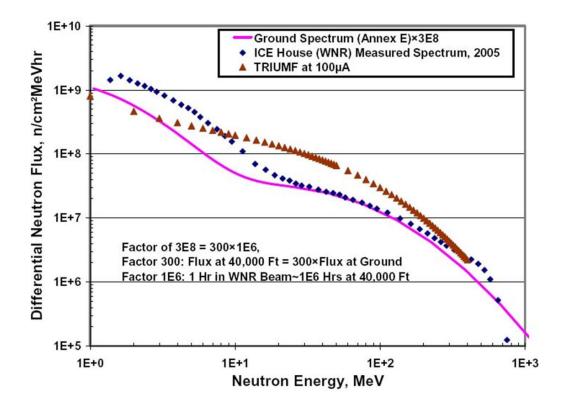

It is possible to perform accelerated neutron testing at one of the following facilties:

- Los Alamos Neutron Science Center (LANSCE) at Los Alamos National Laboratory in Los Alamos, NM.

- Tri-University Meson Facility at the University of British Columbia (TRIUMF) in Vancouver Canada.

- Atmospheric-like Neutrons from thick Target (ANITA) at Svedberg Laboratory, Uppsala University in Uppsala, Sweden.

- Research Center for Nuclear Physics (RCNP) at Osaka University in Osaka, Japan.

- Vesuvio Beamline (ISIS) at Rutherford Appleton Laboratory, Oxfordshire, United Kingdom.

In this work, we used the ICE House at LANSCE to perform accelerated neutron testing [LANSCE, 2011]. The neutron testing is discussed in Section 6.2.1.

#### **Protons**

Atmospheric protons can cause soft errors in electronics. Low-energy protons can be easily absorbed by the atmosphere or most shielding materials and are not a concern for soft errors. At high energy levels (> 100 MeV), protons behave similarly to neutrons in that they generate charge mostly through indirect ionization. However, high-energy proton flux at the ground level (as seen from Figure 2.3) is not very significant compared to the neutron flux, and high-energy protons are often lumped together with high-energy neutrons for study purposes. In the near earth environment, protons are a significant source of radiation, and can both cause soft errors and induce significant long-term damage to electronics similar to transistor aging.

Accelerated proton beam facilities can be found in both dedicated research beam accelerators and cancer treatment facilities, as proton therapy is commonly used for treatment of certain types of cancer such as prostate cancer, pediatric neoplasms, brain cancer and lung cancer. In this study, we performed accelerated proton beam testing at the Indiana University Cyclotron Facility in Bloomington, Indiana [IUCF, 2011]. The proton testing is discussed in Section 6.2.2.

#### **Heavy Ions**

Heavy ions are energetic ionized atoms heavier than helium. Heavy ions are mostly found in the space environment, but can also be found as secondary products of neutron or proton nuclear interaction with silicon, metal or silicon dopants such as <sup>10</sup>B (discussed previously in Section 2.2.2. [Baumann, 2005] When a heavy ion hits silicon, it creates charge only through directly ionization, and becomes completely stopped in silicon. Due to their large size, their energy is entirely transferred to silicon and they can generate substantially more charge than small particles such as neutrons and protons. This work does not consider heavy ions for soft errors, although they also have similar single event effects in electronics.

#### 2.3 Total Dose Effects

When circuits operate for a long time under radiation exposure, they can be subject to slow-varying but lasting effects called Total Dose Effects. Most of the radiation-induced long term damage to CMOS transistors is located in the silicon oxide layer, where additional trap centers are created. Damage to both the field oxide and the gate oxide can change the behavior of transistors, affecting mostly the threshold voltage, leakage current, transconductance (or current gain) of the transistors and noise performance [Wang, 2009, Section 2.3]. In general, radiation dose increases and decreases the threshold voltage of PMOS and NMOS transistors, respectively. For digital circuits, these total-dose effects translate into leakage current (and power) increase, rise/fall transition mismatch (falling transitions become faster while rising transitions become slower) and delay distribution expansion (where the minimum delay path may become faster over time and the maximum delay path slower). These effects are very similar to transistor aging effects in deep submicron processes such as Negative Bias Temperature Instability (NBTI) and Positive Bias Temperature Instability (PBTI).

Although this work primarily deals with radiation effects in the terrestrial environment where total-dose effects are minimal, it is important to note that devices can experience these effects under accelerated radiation testing. Total-dose effects affecting the soft error resilience of sequential circuits are reported in Section 6.2.2.

#### 2.4 Conclusion

This chapter presented an introduction to radiation effects in electronics. Single-event effects, the focus of this work, were divided into soft errors and hard errors. Various soft error terminologies integral to this work were first given, followed by brief descriptions of hard errors such as single-event latchup and single-event gate rupture. To better understand where and how single-event effects occur, various radiation environments and types of radiation particles affecting transistors were described. Accelerated radiation testing offers the possibility of quickly estimating the

soft error performance of electronics within a short time frame. However, total-dose effects, although absent in the normal terrestrial environment, can pose a challenge on circuit operation and performance during accelerated radiation testing, and were later explained in this chapter. To ensure reliable operation of digital circuits, the aforementioned radiation effects, specifically single-event effects, must be taken into account in the design of soft-error-resilient circuits. The following chapter elaborates on various circuit design techniques capable of addressing single-event upsets, and new layout design techniques are developed in Chapter 4. Experimental results from radiation experiments confirm the effectiveness of these design techniques against single-event effects in Chapter 6, and discover new circuit effects caused by radiation effects discussed in this chapter.

## Chapter 3

# Circuit Soft Error Resilience Techniques

Radiation-induced soft errors have been an important design issue for space-bound system applications. A designer can attempt to reduce the number of soft errors by either making individual transistors or circuits more robust to soft errors, or accept that soft errors may occur and use error detection and correction to recover from data corruption. To prevent soft errors from occurring, *Radiation Hardness-By-Design* (RHBD) techniques can be developed at the circuit abstraction level, where the operation of a circuit inherently prevents temporary disruption of a circuit node due to a radiation strike from propagating and generating a soft error.

This chapter presents an overview of existing circuit techniques for soft error resilience. The chapter begins with an introduction on how digital circuit designers traditionally perceive radiation-induced soft errors. Soft errors are then categorized by the type of digital logic where they originate (combinational logic and sequential logic). Soft errors originating from combinational logic typically have substantially lower error rates than those from sequential logic. Therefore, most of the current RHBD efforts are focused on making sequential elements more robust. To give a general understanding of how circuit design can be used to reduce soft errors in sequential logic, this chapter first describes RC-based circuit techniques used to make each circuit node more resistant to charge collection. RC techniques harden a circuit

node by increasing the time constant of the circuit relative to the time constant of single event charge collection. With device scaling, circuits become faster and consume less power, and RC techniques impose a large performance penalty on deep submicron circuits.

Circuit redundancy techniques, described next in this chapter, provide an efficient alternative for reducing soft errors. The main forms of circuit redundancy, such as Triple Modular Redundancy (TMR) and Dual Modular Redundancy (DMR), can offer several orders of magnitude in soft error reduction, by replicating identical circuit elements in the hope that a particle strike will only affect some but not all circuit elements, and the circuit can recover from partial failure by voting on the results of each replicated element. These circuit redundancy schemes can make sequential circuits immune to Single-Event Upsets, or single errors due to radiation strikes affecting on a circuit node. This chapter places more emphasis on DMR due to its lower associated design costs, by describing an assortment of DMR circuit level techniques successfully used in the past or currently in use. The chapter then concludes with a discussion on the shortcomings of the circuit-level soft error resilience techniques, specifically circuit vulnerability to Single-Event Multiple Upsets (SEMUs), where a single particle strike can cause charge collection in multiple circuit nodes.

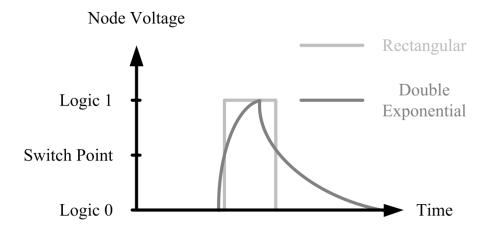

#### 3.1 Soft Error Generation

In the past, circuit techniques for soft-error-resilient sequential cells generally target soft errors due to upsets on a single circuit node, or Single Event Upsets (SEUs). For circuit designers, charge collection on a single circuit node due to a particle strike was thought of as a short duration current pulse producing a voltage glitch, called Single Event Transient (SET). SETs are often modeled as rectangular or double exponential current pulses (see Figure 3.1) [Messenger, 1982], instead of a more accurate current model involving complex device-level simulations such as the one shown in Figure 2.1. For technology nodes with feature sizes larger than  $0.25\mu m$ , this assumption was mostly valid, as Single Event Multiple Upsets (SEMUs), or simultaneous upsets on multiple circuit nodes due to a single particle strike, still formed a small portion of

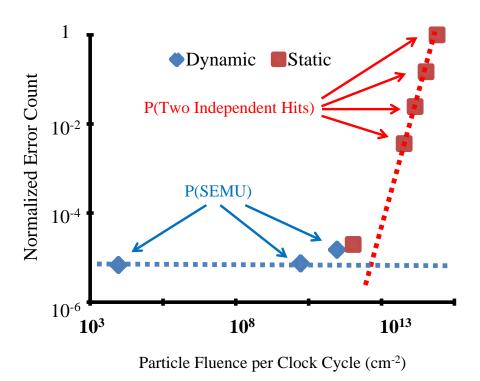

the overall Soft Error Rate (SER) (see Figure 3.2) [Seifert et al., 2006].

The proportion of SEMUs in all soft errors increases exponentially as device dimensions and distances are reduced. Chapter 4 addresses the growing SEMU concern through transistor layout techniques.

Soft errors can be categorized in two groups: soft errors in combinational logic and soft errors in sequential logic. A soft error can be generated when a particle hit produces a SET (glitch) on a combinational logic gate: the SET can propagate down the combinational path and become latched by a sequential cell, producing a soft error (Figure 3.3) [Mavis and Eaton, 2002; Dodd and Massengill, 2003].

In order for the SET in the combinational logic to produce a soft error, several conditions must be satisfied:

- 1. The produced SET must be a voltage pulse with sufficient amplitude (larger than the input noise margin) and duration to propagate downstream.

- 2. The logic path leading to the sequential cell must be sensitized to allow the SET to propagate to the input of the sequential cell.

- 3. The SET must arrive at the data input of the sequential cell inside the cell's vulnerable input latching window (Figure 3.4).

However, combinational soft errors still form a very small portion of the overall soft error rate, and typical soft error resilience strategies target sequential soft errors. When an energetic particle strikes a sequential cell in its retention state, sufficient charge can be collected by the circuit node storing the memory content and alter the memory state. To prevent soft errors in sequential cells, we can harden individual circuit nodes to make them more resilient to charge collection. The likelihood that an individual node becomes upset depends on its node capacitance, the voltage difference needed to flip its logic value as well as the strength (or lack) of the driver maintaining the node voltage. Resistor- and capacitor-based techniques discussed in Section 3.2 can reduce the soft error rate by targeting these conditions to protect against individual node upsets, but they do not provide full immunity against SEUs and can affect circuit performance. It is possible to make sequential cells fully SEU-immune

Figure 3.1: Rectangular and double exponential pulse models for single event transients.

Figure 3.2: Comparison of published single-event multiple upset probabilities (adapted from  $Seifert\ et\ al.\ [2006].$

Figure 3.3: Combinational and sequential soft errors from *Dodd and Massengill* [2003].

by making use of circuit node redundancy (i.e. storage the same memory bit in multiple locations). Sections 3.3 and 3.4 present efficient SEU-immune redundancy-based circuit techniques where circuit nodes are replicated, and single errors among multiple copies of the same node can be detected and corrected. Table 3.1 summarizes the RC-based and redundancy-based circuit techniques to be discussed in this chapter.

## 3.2 RC-Based Soft Error Resilience Techniques

To understand how to design radiation-hardened sequential elements, one must first understand how sequential elements in general respond to radiation-induced charge collection. CMOS memory storage elements can have their data content temporarily stored as floating charge (for example, in a capacitor in a Dynamic Random Access

Figure 3.4: Vulnerable timing window for combinational SETs latching into sequential cells *Mavis and Eaton* [2002].

Memory (DRAM) cell or in a floating gate in Flash Memory), or maintained by an active feedback circuitry (such as a pair of cross-coupled inverters in static latch or a Static Random Access Memory (SRAM) Cell).

DRAM cells typically have more compact cell area due to the lack of feedback circuitry, but are prone to bitline current leakage as well radiation-induced collection impacting their stored charge. Therefore, most DRAM memory arrays have frequent charge refresh cycles as well as built-in Error Correcting Code (ECC) circuitry, and do not in general require additional circuit hardening beyond the built-in error correction circuitry. Due to the constant memory refresh of DRAM cells, the soft error rate of DRAM is about two orders of magnitude lower than SRAM [Doucin et al., 1997].

CMOS flash memory is more resilient to single-event charge collection compared to SRAM or DRAM, since the floating gate in each cell is not electrically connected to the semiconductor substrate or junctions where most of the radiation-induced charge collection occurs [Doucin et al., 1997; Fogle et al., 2004]. However, the floating gate structures are sensitive to voltage threshold shifts and leakage current due to long term

| Family                                 | Technique                                       | Design                                    | Description                                                                  |

|----------------------------------------|-------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|

| Triple Modular Redundancy (TMR)        | Spatial<br>Sampling                             | Spatial<br>Sampling Latch <sup>(1)</sup>  | Triplication of storage elements with a majority voter at the output.        |

|                                        | Temporal<br>Sampling                            | Temporal<br>Sampling Latch <sup>(1)</sup> | Three time-delayed storage nodes filtered with 3-input majority voter.       |

| Dual<br>Modular<br>Redundancy<br>(DMR) | C-Element                                       | Guard Gate <sup>(2)</sup>                 | SET filter by comparing a signal and its delayed copy.                       |

|                                        |                                                 | BISER <sup>(3)</sup>                      | Duplicated unprotected storage elements and C-Element voter with keeper.     |

|                                        |                                                 | 4-TAG <sup>(4)</sup>                      | Modified latch with built-in keeperless C-Elements in duplicated loop paths. |

|                                        | Half-Transition<br>NAND gate                    | $SERT^{(5)}$                              | Latch modified from 4-TAG.                                                   |

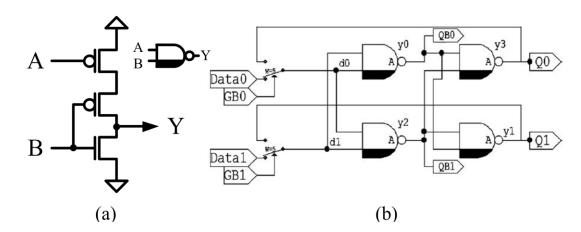

|                                        | Differential<br>Cascode Voltage<br>Switch Logic | $\mathrm{DCVSL}^{(6)}$                    | Duplicated circuit nodes for every logic gate.                               |

|                                        | Dual-<br>Interlocked<br>Storage Cell            | DICE <sup>(7)</sup>                       | Modified latch with duplicated circuit nodes.                                |

Table 3.1: Overview of circuit-level techniques for soft error resilience<sup>1</sup>.

ionizing dose exposure, and soft error rates increase substantially with increasing total dose exposure [Nguyen et al., 1999; Nguyen and Sheik, 2003; Bagatin et al., 2010]. The discussion on the impact of radiation damage on flash memory is outside the scope of this work.

Most sequential cells maintain their data content by actively driving them in a feedback circuit loop. The simplest form of sequential cell is a pair of cross-coupled inverters storing a single bit in an SRAM cell, shown in Figure 3.5. In this circuit configuration, a memory bit is stored as a voltage and its complement in circuit nodes A and B. When a radiation strike hits an "off" NMOS transistor (called "struck transistor"), negative charge collects on its drain node, creating a negative voltage transient on the drain node and potentially upsetting the logic-high value of node A.

<sup>1(1)</sup> Mavis and Eaton [2002]. (2) Balasubramanian et al. [2005]. (3) Mitra et al. [2005]. (4) Shuler et al. [2005]. (5) Shuler et al. [2009]. (6) Casey et al. [2005]. (7) Calin et al. [1996].

Figure 3.5: SEU response model in an SRAM cell adapted from *Dodd and Massengill* [2003].

This initial charge collection step is represented by the first exponential of the double exponential model in Figure 3.1. If the collected charge does not reach the critical charge level (the minimum charge required to upset the memory cell, often labeled as  $Q_{\rm crit}$  or  $Q_{\rm c}$ ) [Dodd and Sexton, 1995], the "on" PMOS transistor, connected to the "off" NMOS transistor by its drain node and acting as a "restoring transistor" will remove the excess charge and restore the circuit node voltage connecting both "struck transistor" and "restoring transistor." The restoring action is represented by the second exponential of the double exponential model in Figure 3.1. However, if the radiation-induced charge collection exceeds the critical charge, the "restoring transistor" may not recover the upset drain node voltage in time, and the upset node voltage can propagate to the complementary circuit node B through the opposite inverter circuit feedback and flip the overall stored bit (i.e. both circuit node A and B are upset).

The likelihood that the SRAM cell is upset depends on the amount of charge deposited, the capacitance of the affected circuit node and the drive strength of the restoring transistor. The goal of hardening the SRAM cell against single-event inducing radiation strikes is to reduce the width and/or amplitude of the transient

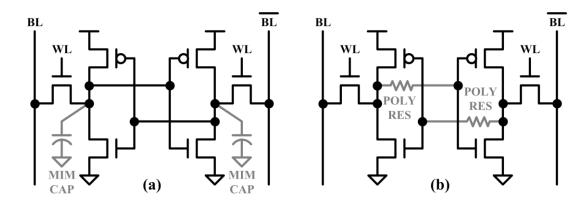

Figure 3.6: RC-hardened SRAM cells. (a) Hardened SRAM cell using Metal-Insulator-Metal capacitors. (b) Hardened SRAM cell using highly resistive polysilicon resistors.

voltage pulse so that the SRAM cell becomes less sensitive to charge collection. One way to improve the soft error resilience of the SRAM cell is to substantially increase the storage node capacitance in each cell without any area impact by introducing a Metal-Insulator-Metal (MIM) capacitor between the polysilicon and Metal 1 layers of the cell [Geppart, 2004; Roche et al., 2004; Roche et al., 2005; Lysinger et al., 2008] (Figure 3.6a). It is also possible to harden the SRAM cell by adding intracell decoupling polysilicon resistors in series with the gate terminal of each inverter inside the SRAM cell, as shown in Figure 3.6b [Diehl et al., 1982; Weaver et al., 1987; Rockett, 1992]. Both the addition of high density capacitors and resistors require silicon process enhancement, and are not covered in this work. Moreover, these techniques do not provide full immunity against SEUs, and it is possible to make cells even more robust without any special process enhancement using redundancy-based techniques to be discussed in the next two sections.

## 3.3 Triple Modular Redundancy

Most of the effort on circuit-level soft error mitigation techniques in the past two decades has been on providing full immunity to single soft errors through circuit redundancy. The most popular technique, called *Triple Modular Redundancy* (TMR),

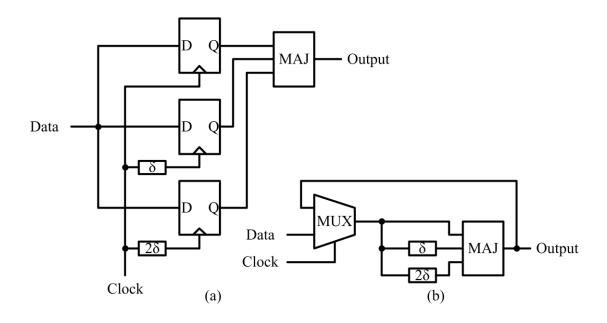

Figure 3.7: Triple modular redundancy latches from *Mavis and Eaton* [2002]. (a) Spatial sampling latch. (b) Temporal sampling latch.

involves replicating a storage node three times and adding a three-input majority gate to filter out unwanted SETs or SEUs [Mavis and Eaton, 2002]. When a single error occurs in any of the three storage nodes, a three-input majority gate can recover the correct value through voting. Figure 3.7 shows two implementations of Triple Modular Redundancy. Spatial Sampling (shown in Figure 3.7a) involves the use of three identical latches (or flip-flops) to store one memory bit. Whenever a single error occurs in any of the three elements, the majority gate at the output can recover the correct result.

The use of delay elements with delay  $\delta$  and  $2\delta$  to create three delayed versions of the clock for sampling, also called *Temporal Sampling*, can prevent SETs on the clock and data inputs, of widths smaller than  $\delta$ , from simultaneously corrupting the three storage elements, since each latch or flip-flop now samples at clock edges separated by  $\delta$  in time. Temporal sampling can also be incorporated directly into the latch structure by replicating the storage node in time using the same delay elements (Figure 3.7b).

Triple Modular Redundancy, especially using spatial sampling such as Figure 3.7a, is popular among ASIC (Application Specific Integrated Circuit) and FPGA (Field Programmable Gate Array) designers, since it does not introduce any new circuit element to the existing standard cell library. However, TMR requires at least 3X area cost, 3X power cost and moderate delay cost due to the triplication of the sequential cells and the addition of the delay elements and majority gate.

## 3.4 Dual Modular Redundancy

In order to achieve the same soft error resilience as TMR but with less area and power cost, we can incorporate Dual Modular Redundancy, or DMR, in sequential cell design [Calin et al., 1996; Shuler et al., 2005; Mitra et al., 2005; Casey et al., 2005]. The main idea behind DMR is to use duplicated circuit elements as a form of redundancy to obtain soft error resilience, and in general the power and area cost required is slightly higher than double that of a regular design. Though capable of achieving near identical soft error resilience as TMR at a much reduced area and power cost, DMR has not been incorporated in standard ASIC design flow where the majority of IC design is based upon, as DMR requires specialized circuit designs outside the standard cell library typically provided by ASIC vendors. Also, for large memory arrays, error correcting codes can replace the need for having individual hardened memory cells. Despite the limited use of DMR, DMR has a rich assortment of circuit techniques that can address SEUs, and it is worth studying these techniques to understand how interactions between transistors in a redundant circuit can protect against soft errors. Chapter 4 takes inspiration from these circuit interactions to develop new ways of placing individual transistors to stress these interactions to improve the soft error resilience of the circuit.

#### 3.4.1 C-Element Based Soft-Error-Resilient Latches

When we discussed TMR in the previous section, the first thing that came to mind was the three-input voter capable of filtering out one error stored in three memory

Figure 3.8: The C-Element. (a) Circuit implementation with optional keeper. (b) Truth table. (c) Symbolic representation [Muller and Bartky, 1959].

elements storing the same bit. One wonders whether it is possible to do so with only two memory elements (i.e. DMR). If indeed a single upset happens in one of the memory elements, we can only observe that both elements contain different bits, but we cannot determine which element is erroneous. But what if we *knew* what the correct value should be before the single upset?

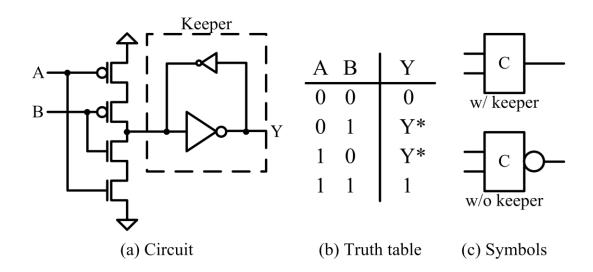

Muller and Bartky [1959] developed the C-Element in asynchronous circuit theory as a two-input SET filter capable of correcting single upsets in DMR-based designs (replacement for the three-input majority voter found in TMR). The C-Element passes the value of its inputs to its output when both inputs are equal, or retains its previous output value otherwise (Figure 3.8a). Figure 3.8b shows the logic function of C-Element, and Figure 3.8c shows the symbols for the C-Element used in this thesis. The keeper-less C-Element in Figure 3.8c is sometimes called a "Guard Gate" or a "transition NAND Gate", and is much more vulnerable to circuit noise due to the lack of the keeper [Balasubramaian et al., 2005; Shuler et al., 2006].

The C-Element can be used to filter out unwanted SETs in combinational logic entering a sequential element, as shown in Figure 3.9. In this case, any SET of duration less than  $\delta$  produced in the combinational logic or at the inputs to the

Figure 3.9: SET filtering of a latch input using C-Element from *Balasubramanian et al.* [2005].

C-Element cannot propagate to the latch input. However, this configuration is still vulnerable to SETs with pulse widths larger than  $\delta$ , as well as SETs produced by a particle strike on the output of the C-Element. In some cases, the contribution of SETs from the combinational logic block can be large enough to merit the use of guard gate as an effective SET suppression method.

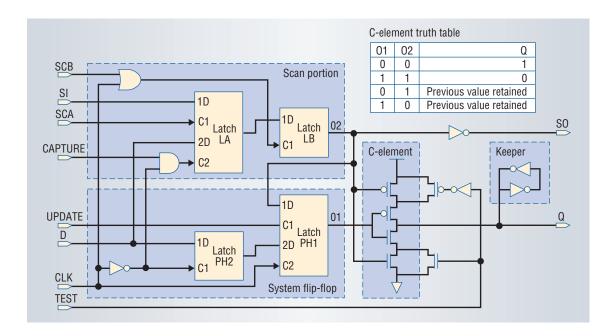

By using the C-Element to vote on the outputs of two identical unhardened master-slave flip-flops, we can construct a soft-error-resilient sequential element called Single C-Element Dual Modular Redundancy (SCDMR) flip-flop (Figure 3.10), similar to the BISER flip-flop from *Mitra et al.* [2005] and *Zhang et al.* [2006]. Like the TMR scheme described in Section 3.3, SCDMR uses voting to detect and correct single errors: the two-input C-element acts as the two-input voting gate for two identical flip-flops. The soft error resilience of SCDMR is based on the idea that whenever a mismatch occurs at the outputs of the duplicated storage elements, the C-Element voting circuit blocks the outputs of the identical flip-flops and the keeper retains the previous correct value. When the C-Element is in blocking mode (its inputs are different), the keeper acts as a temporary storage for the previously correct value (before any error occurred on one of the latches), and any additional upset on the keeper can permanently change the output of the sequential cell.

Figure 3.10: Single C-Element Dual Modular Redundancy (SCDMR) master-slave flip-flop.

The SCDMR flip-flop also has an additional vulnerability to upsets occurring simultaneously or separately on both flip-flops, as the identical unhardened latches themselves have no ability to recover themselves. While operating in high clock frequencies (> MHz), upsets in the SCDMR flip-flops are dominated by SEMUs. If the SCDMR latch operates in very low frequencies (<< Hz) or remains in a retention (opaque) mode where the clock is disabled for some time (this can be the case if the circuit is in standby mode), different upsets due to different particle strikes can upset this sequential element.

Despite the more than double area/power penalty and moderate delay penalty imposed on SCDMR due to the presence of two identical flip-flops and the C-Element, the cost impact of SCDMR can be greatly reduced by reusing existing on-chip scan design-for-testability resources within microprocessors. *Mitra et al.* [2005] presented the *Built-In Soft Error Resilience* (BISER) flip-flop, where the existing scan flip-flop is re-equipped with a C-Element voting gate at its output and small changes to its input to provide soft error protection with minor costs (Figure 3.11). *Zhang et al.* [2006] provided a detailed description of different operational modes for this flip-flop.

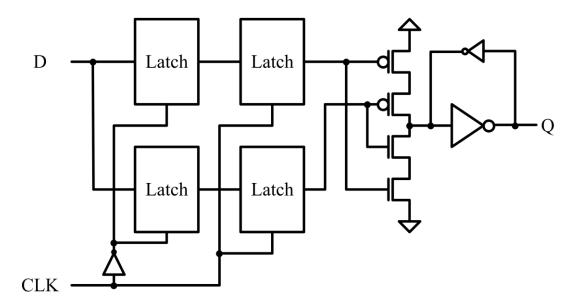

Figure 3.11: Built-In Soft Error Resilience (BISER) flip-flop from *Mitra et al.* [2005].

Radiation experiments in 45nm bulk CMOS demonstrate that BISER can have soft error resilience "in excess of 100X with respect to non-hardened designs" [Seifert, 2008].

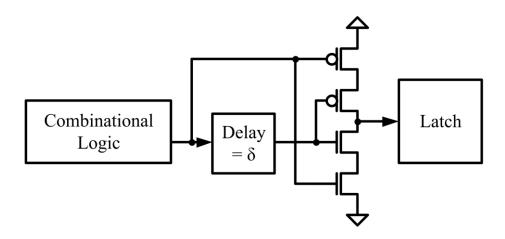

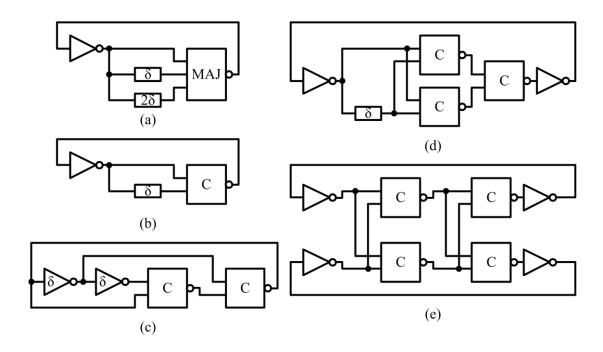

A different approach to improving the soft error resilience of a flip-flop using C-Elements is to incorporate delay filtering with keeper-less C-Elements in the feed-forward path of a latch. The keeper-less C-Elements are also called Guard Gates [e.g., Balasubramanian et al., 2005] or Transition AND Gates (TAG) [e.g., Shuler et al., 2005]. The TMR temporal sampling latch from Figure 3.7b is a typical example of delay filtering in feedforward path of a soft-error-resilient latch, where the original latch signal is replicated 3 times in time to allow removal of any SET with pulse duration less than the delay of the delay element,  $\delta$ , by the 3-input majority voting gate. During the opaque (or retention) mode of this latch, the overall latch can be reduced to the circuit shown in Figure 3.12a. To transform this TMR temporal sampling latch into a DMR latch to reduce design costs, we can replace the 3-input majority voting gate with a 2-input keeper-less C-Element to produce a DMR temporal sampling latch called "1-TAG" shown in Figure 3.12b [Shuler et al., 2005]. The

Figure 3.12: Delay filtering in the feedforward path of soft-error-resilient latches. (a) TMR temporal sampling latch. (b) 1-TAG from *Shuler et al.* [2006]. (c) Enhanced Delay-Filtering (EDF) latch (this work). (d) 3-TAG from *Shuler et al.* [2006]. (e) 4-TAG from *Shuler et al.* [2005].

"1-TAG" latch is significantly less soft-error-resilient compared to the TMR Temporal Sampling Latch, since any SET arriving at the inputs of the C-Element can render the C-Element output temporarily undriven (floating) and prone to any additional single-event charge collection.

To improve the soft error resilience of the "1-TAG" latch, we can create more complex latches using two logic levels of keeperless C-Elements, such as the "EDF" latch (Figure 3.12c, e.g. this work), the "3-TAG" latch (Figure 3.12d) [e.g., Shuler et al., 2006] and the "4-TAG" latch (Figure 3.12e) [e.g., Shuler et al., 2005; Shuler et al., 2006]. Heavy ion experiments in  $0.35\mu$ m bulk CMOS show that the "1-TAG" and "3-TAG" exhibit 3.2X and 6.6X soft error reduction, significantly less than the 100X soft error reduction expected from typical DMR circuit techniques. However, the same study also shows that the "4-TAG" latch performs substantially better, with only a single error observed during the entire course of the experiment. The difference

in soft error resilience between the various "TAG" designs can be explained by the following observations:

- 1. Both the "1-TAG" and "3-TAG" designs are at not immune to SEUs created from SETs on a single node with duration longer than  $\delta$ , the delay of the delay element used.

- 2. The "4-TAG" design is instead immune to ALL SEUs regardless of SET duration, because every circuit node in the design is duplicated. The SEU immunity restricts the range of possible strike angles that can upset this design.

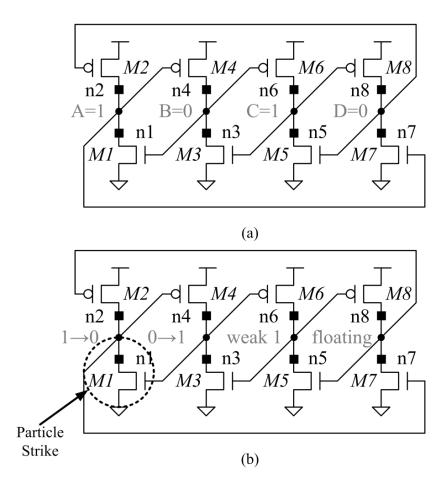

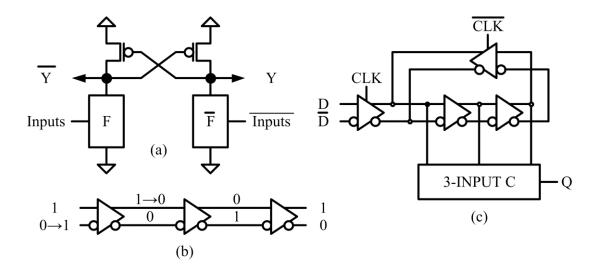

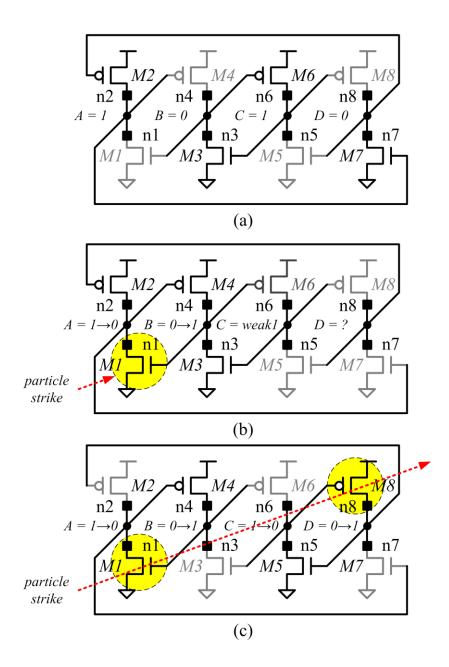

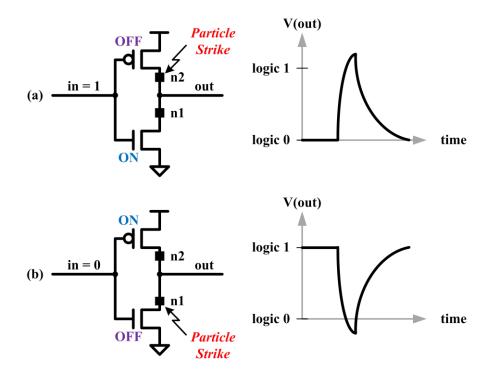

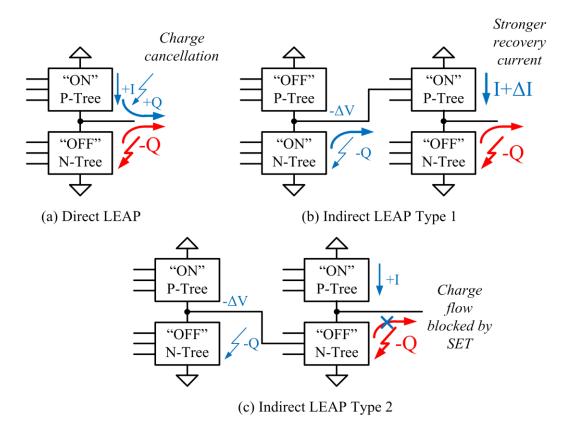

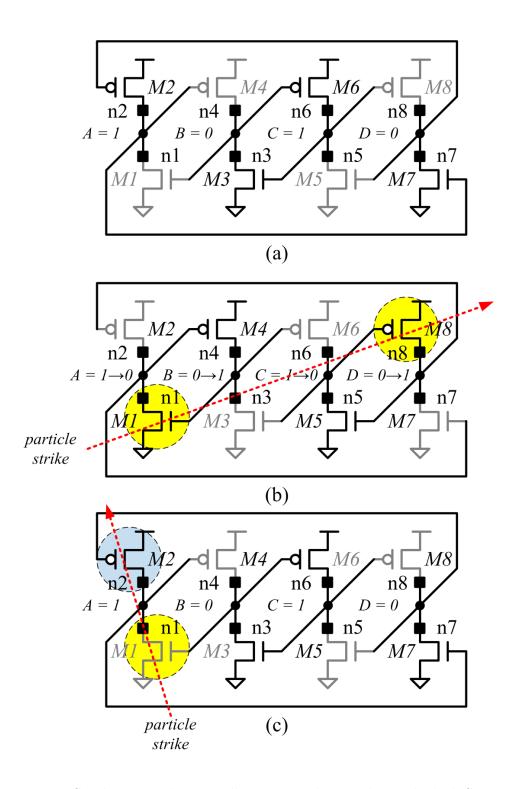

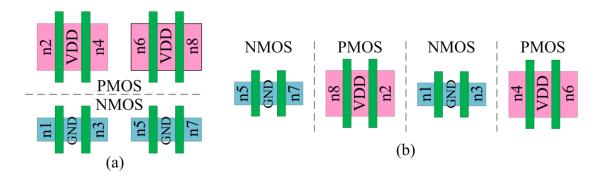

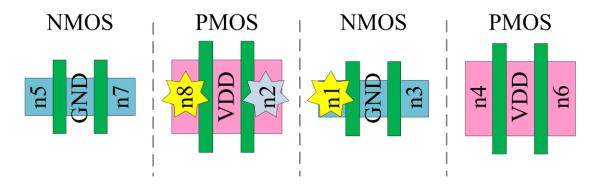

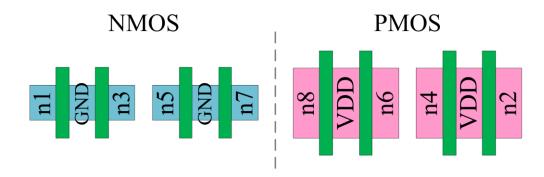

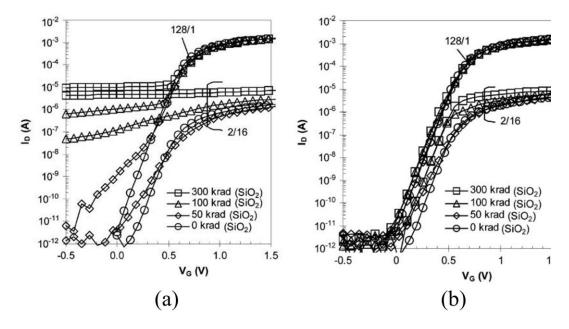

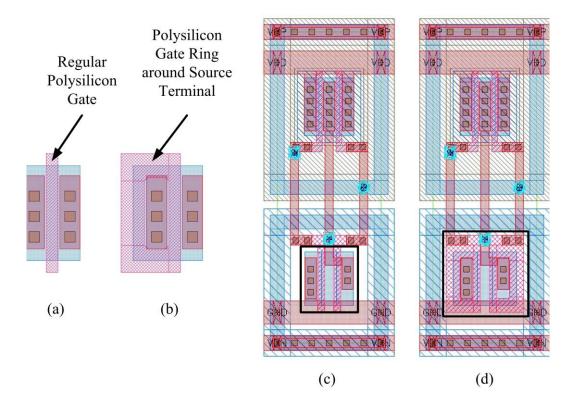

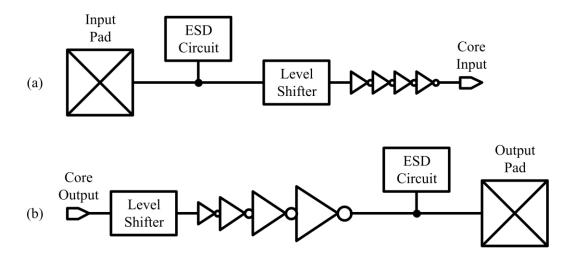

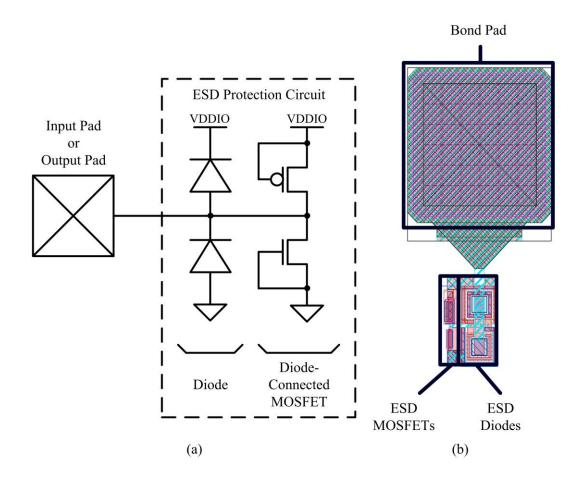

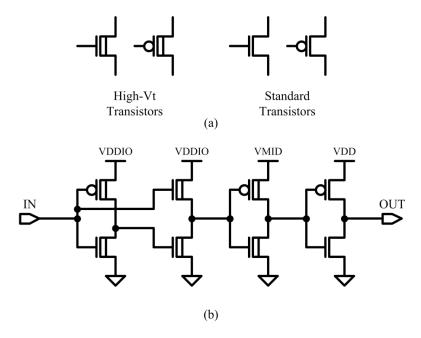

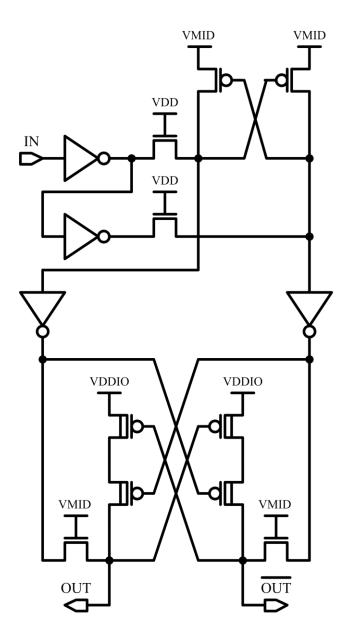

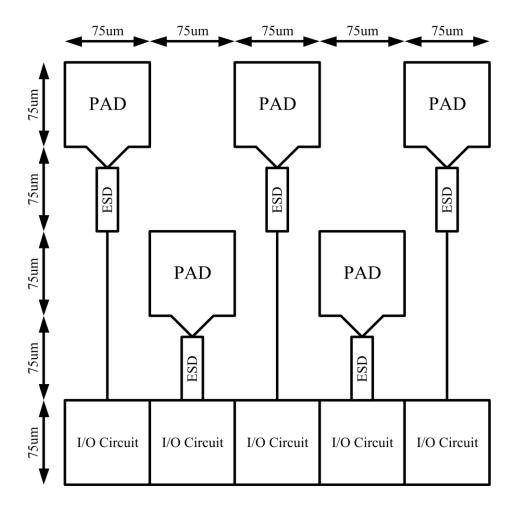

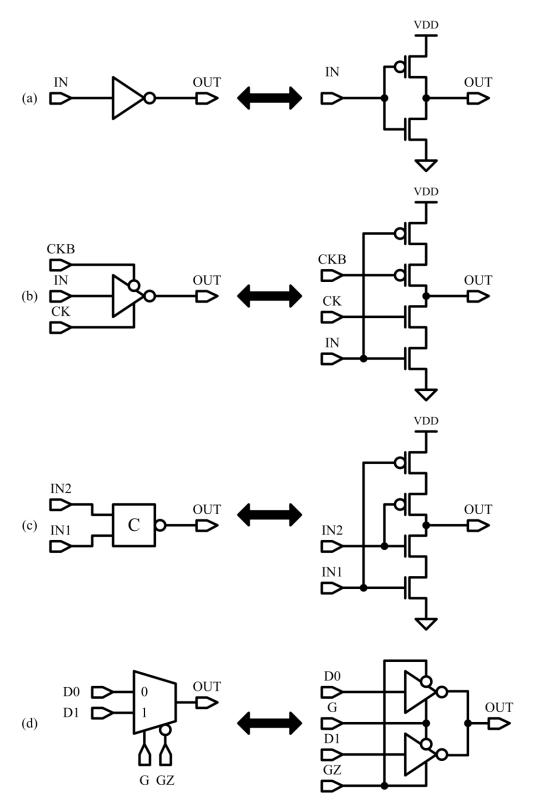

- 3. Circuit simulations also show that the "4-TAG" design has an inherently higher critical charge on its sensitive nodes compared to the other designs.